January 19, 2020

Master the three prerequisites of format translation and chose the right one from the various translation strategies.

October 9, 2019

Learn how XML-based constraints can standardize rule development and use with coding examples for the Calibre PERC reliability platform.

September 13, 2019

SEMICON West showed a distinct thematic shift away from preserving Moore's Law to assessing the architectural implications of AI, as EDA was brought into the event.

July 27, 2019

Whether you use OASIS or GDSII, unwanted duplicate cells can make their way into the final SoC database. Learn how to remove them.

May 21, 2019

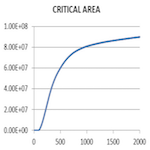

How Mentor develops and works with partners to prepare each version of its Calibre DFM platform to be ready for the introduction of each new process node.

April 15, 2019

CAA is a valuable tool available to both design engineers and foundries to help them avoid layout-dependent effects during manufacturing.

March 25, 2019

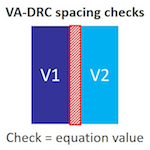

Automated voltage-aware DRC addresses the reliability verification challenges in today’s high-voltage and multiple power domain applications.

March 13, 2019

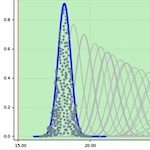

Machine learning techniques help ensure the validity of Liberty Variation Format information for OCV analysis at lower process nodes.

February 8, 2019

How to achieve efficient merging of data from formats such as OASIS, GDS, and OpenAccess to ensure timely verification through DRC runs.

December 31, 2018

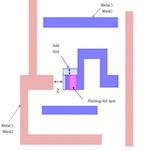

A detailed dive into how MBH strategies for litho hotspots have been enhanced to deal with double patterning at 20nm and below.