October 6, 2022

3D-IC presents major connectivity challenges in maintaining a golden netlist and managing necessary exceptions. Learn how to manage them.

May 10, 2022

Coordinate-based checking provides a streamlined way to verify designs around ESD before full-chip runs without the need for custom checks.

November 12, 2021

Pre- and post-processing EDA techniques help streamline design rule checks and delivery efficient waivers to speed design and debug.

July 20, 2021

How to carry out a sensible analysis of cloud EDA's potential, so you get the right tools and computational resources to deliver increasingly complex designs.

June 21, 2021

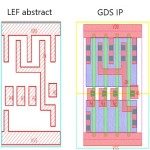

Overcome problems created by mismatches between library exchange format (LEF) and GDS or OASIS representations to avoid design delays.

December 9, 2020

Invocation GUIs play an important role in delivering efficient verification runs. Learn how to take advantage of the features within Calibre Interactive.

October 16, 2020

Reliability rule checks need - and now get - more granular analysis that allows designers to adopt proposed waivers with much greater confidence.

September 21, 2020

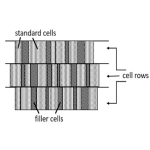

A physical verification-ready flow can speed project delivery by making your use of filler cells more efficient.

August 25, 2020

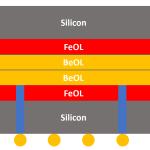

How Calibre is evolving to address the challenges of LVS verification in early-stage design.

August 14, 2020

For physical verification and beyond, each process node requires new thinking, new tools and greater performance.