May 31, 2021

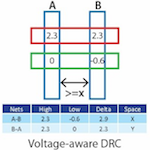

Using on-demand rule checks during place-and-route boosts efficiency and design quality.

September 21, 2020

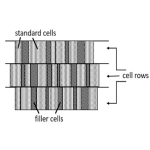

A physical verification-ready flow can speed project delivery by making your use of filler cells more efficient.

August 14, 2020

For physical verification and beyond, each process node requires new thinking, new tools and greater performance.

May 21, 2019

How Mentor develops and works with partners to prepare each version of its Calibre DFM platform to be ready for the introduction of each new process node.

November 20, 2018

Adoption of high-density advanced packaging (HDAP) needs tools and supports to build designers' confidence in the emerging technology.

October 16, 2018

How you can use the dedicated rule decks now being provided by foundries as the foundation for a reliability verification flow.

August 13, 2018

Dina Medhat describes what you need to know about the types of waiver strategy that can be applied.

September 14, 2017

An alphabet soup of AI, HPC, 5G and the IoT has finally seeded creation of a design infrastructure for silicon photonics.

April 28, 2014

The encryption chain for today's highly collaborative designs needs to be managed with care.

June 1, 2012

There's still debate over certain aspects of the 20nm node, but the main challenges are already being addressed. Expect to see foundries and vendors mark their turf at DAC.