Use evolving DRC to automate high-voltage and multi-power domain verification

Automated voltage-aware DRC addresses the reliability verification challenges in today’s high-voltage and multiple power domain applications.

The evolution toward voltage-aware DRC

Companies designing high-voltage and multiple power domain applications at established and emerging nodes must achieve exacting accuracy to achieve the reliability and yields required by their target markets. Enhanced voltage-aware design rule checking (VA-DRC) delivers an automated verification flow that provides precise, accurate, and actionable, context-aware results needed to meet tight schedules and the demands from constant innovation.

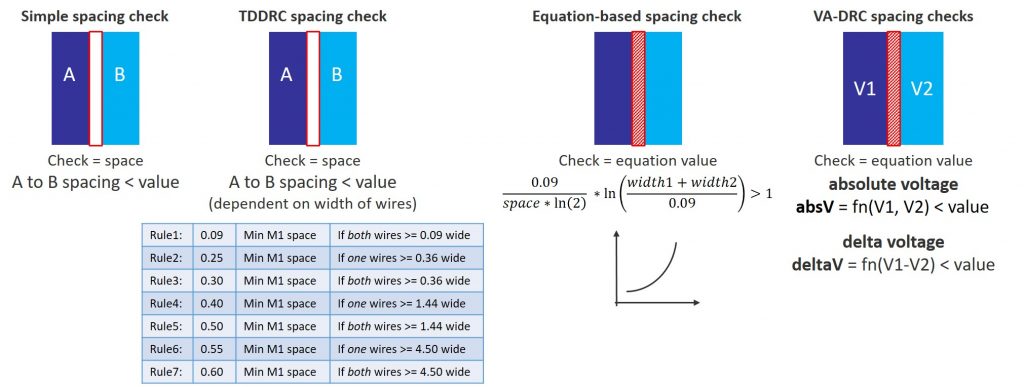

DRC spacing checks increase significantly in complexity at each new process node. More and smaller features in less space means that new effects emerge and minor effects become significant. To address the ever-tighter tolerances of design properties such as run lengths and wire widths, traditional spacing checks first evolved into the use of table-driven DRC (TDDRC) to account for a range of dimensions. TDDRC helped ease the readability and maintenance of an exploding number of discrete parameter combinations. But the need to cover continuous relations between parameters required a further evolution toward equation-based DRC (eqDRC). It could more accurately evaluate curves and complex equations [1].

As it turned out, that wasn’t all eqDRC was good for. At both established and emerging nodes, today’s designs often have many power domains in which a high-voltage net is routed closely to a low-voltage net. Ever more complex applications must operate effectively within these multi-power domain designs. But particularly for new technologies, more tightly packed layouts are having an impact on reliability because of complex interactions between the voltage domains. The development of eqDRC presaged the next evolution, bringing a solution for these composite spacing requirements that draws upon both electrical and physical information. We call this latest evolution ‘voltage-aware DRC’ (VA-DRC).

VA-DRC checks combine physical and electrical analysis. It uses either absolute voltage or difference/delta voltage (DV) values to check spacing requirement compliance. This helps ensure that designs comply with all process, reliability, and power management requirements [2][3].

Figure 1 shows the evolution in spacing checks from the simplest fixed measurement to VA-DRC checks that can calculate the correct spacing based on voltage values.

Figure 1. DRC spacing checks have evolved to meet changing demands in design verification (Mentor – click to enlarge)

Voltage-aware DRC checking

The essential element of VA-DRC is its ability to incorporate voltage information into the physical check.

Early VA-DRC flows used manual markers to annotate polygons with their voltage domain information. That approach may still be manageable for a few designs at some established nodes. But we are now seeing rises in complex multi-power domain design, and the need to fit more functionality into the same or smaller design areas. Here, manual annotation very quickly explodes in complexity. It also becomes unacceptably prone to human error. Sometimes the markers are forgotten or they touch the wrong polygons. In later design phases (after several levels of hierarchy integration), these markers or properties often become contradictory.

Automated context-aware voltage propagation and annotation eliminates human error and improves the accuracy of VA-DRC spacing. Because it can use both design front-end (source netlist) and design back-end (layout) information simultaneously, a reliability platform like Calibre PERC can support automated VA-DRC spacing checks that quickly and accurately analyze the voltage domains of each polygon/net. It can then determine the correct spacing based on the absolute voltages or DV of those nets.

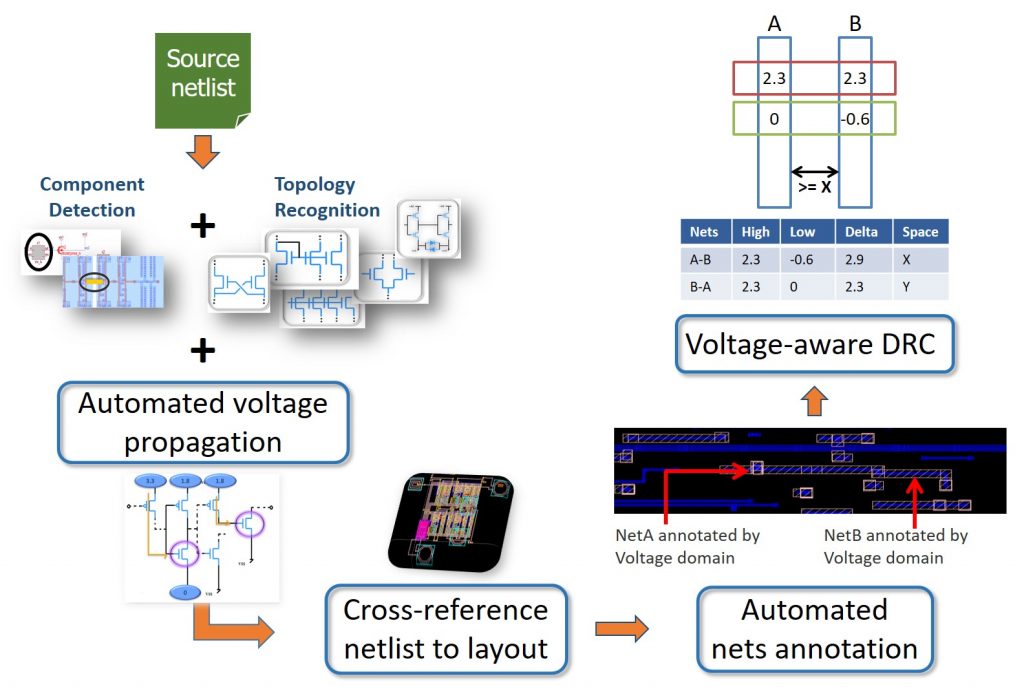

The Calibre PERC VA-DRC flow propagates voltages statically from the top ports to determine the correct voltage domain on the netlist level, cross-references the netlist to the layout, then annotates the nets or devices of interest before cross-referencing the netlist to the layout side to perform the spacing checks (Figure 2).

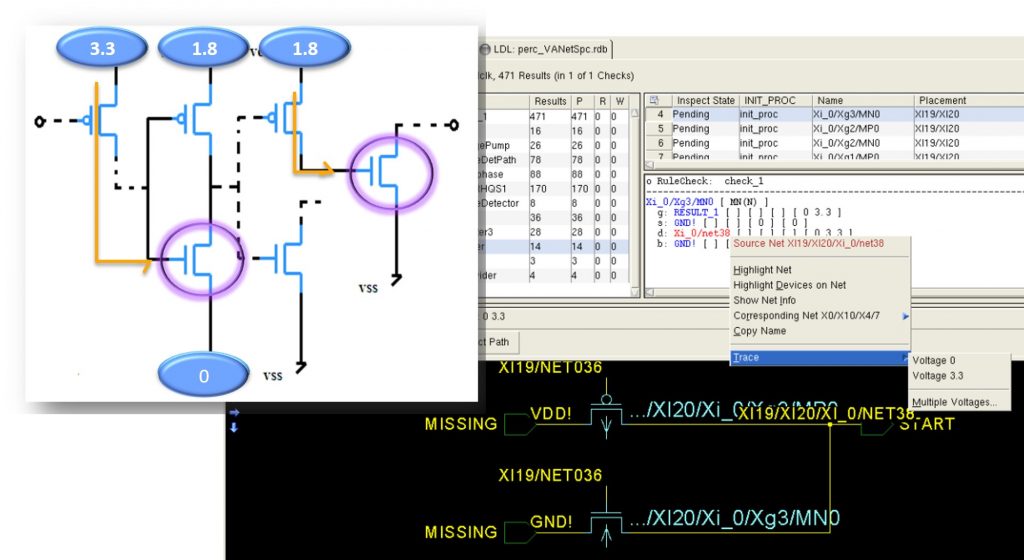

The automated voltage propagation uses the top-level port voltages as inputs. Using a static voltage propagation technique, the tool can apply voltage drop, as well as directional propagation and conditions [4]. Each net in the topological results is displayed with its voltage domains so designers can quickly trace the source of the voltage propagation (Figure 3).

Figure 3. Static voltage propagation improves annotation by adding voltage propagation detail (Mentor – click to enlarge)

The improved accuracy that can be achieved with automated, context-aware VA-DRC is essential for reliability verification in high-voltage applications to ensure high design reliability and manufacturing yield.

Voltage-aware DRC debugging

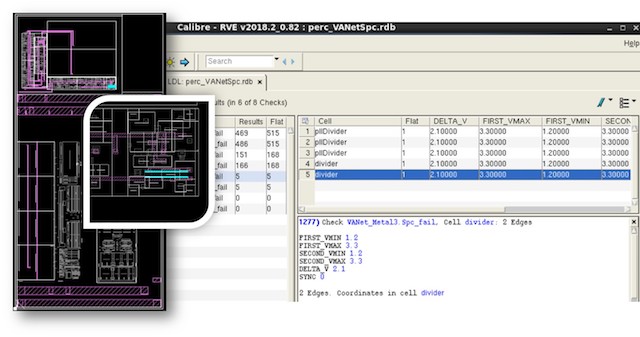

The other challenge in applying traditional VA-DRC lies in the interpretation and debugging of the error results. A manual annotation approach relies on polygons for geometrical debugging (Figure 4). Without any information about the nets or voltage domains involved in the violation, debugging these errors is time-consuming and frustrating. The fixes often include guesswork.

Figure 4. Traditional voltage-aware DRC results only show spacing violations between polygons (Mentor)

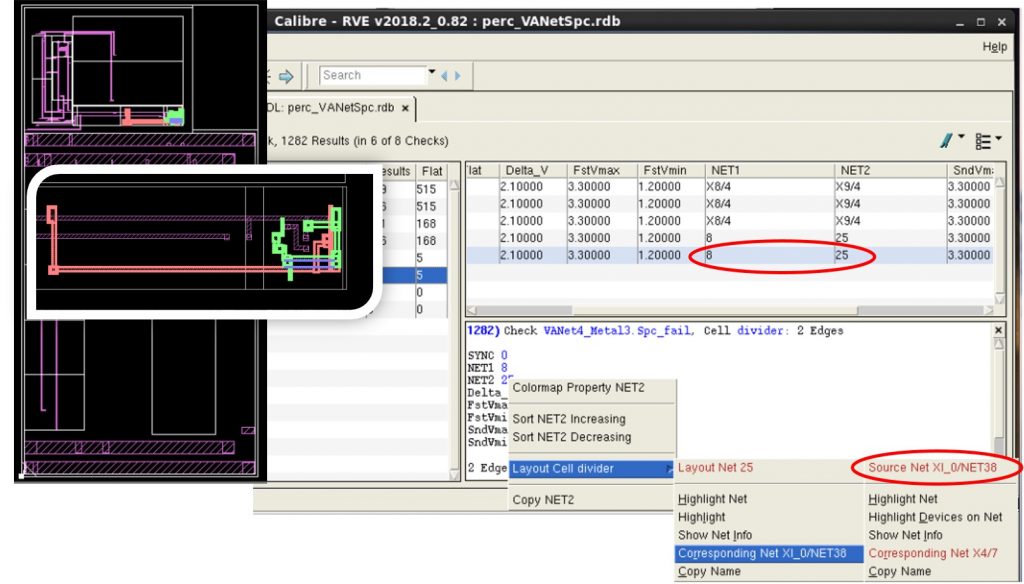

With its ability to trace and debug both physical and electrical information within a results viewing interface, the Calibre PERC automated VA-DRC flow supports augmented debugging and error fixing. Automated VA-DRC results attach a net-name property for each edge of the edge-pairs. This gives designers the necessary electrical awareness information to trace and debug violations (in source-based flows) based on the source net and instance names (Figure 5). The context-aware aspect of these enhanced VA-DRC checks provides actionable results that can be used to make educated decisions when implementing fixes.

Figure 5. Automated voltage-aware DRC delivers both physical and electrical information for faster, more precise debugging (Mentor – click to enlarge).

Conclusion

With an automated flow that can propagate accurate voltage values based on static propagation rules, the Calibre PERC automated VA-DRC functionality exceeds the accuracy of both traditional geometric checks and manually annotated VA-DRC. It also provides actionable, context-aware information to the designers to support more accurate and efficient debugging and reinforce reliability optimization strategies. With this improved accuracy, and actionable, context-aware results that support informed debugging, engineers can use an automated VA-DRC flow to deliver productivity, precision, and reliability—critical elements of success in markets driven by tight schedules and constant innovation.

Further reading

To learn more about the enhanced context-aware VA-DRC functionality in Calibre PERC, download this white paper: Calibre PERC advanced voltage-aware DRC delivers exacting accuracy for today’s complex designs.

References

[1] David Abercrombie and John Ferguson. “Equation-based DRC: A novel approach to resolving complex nanometer design issues,” Mentor, a Siemens Business. February 2009.

[2] Matthew Hogan. “Improve reliability with accurate voltage-aware DRC,” Mentor, a Siemens Business. September, 2013.

[3] Dina Medhat. “Automated Solution for Voltage-Aware DRC.” EE Times, SOC DesignLines. Dec 23, 2015. https://www.eetimes.com/author.asp?section_id=36&doc_id=1328540

[4] Frank Feng. “Full-Chip Electrical Reliability Verification: A New Approach for Advanced Nodes,” Mentor, a Siemens Business. October, 2017.

[5] Dina Medhat. “Protecting Against IC Reliability Failures with Automated Voltage Propagation,” Mentor, a Siemens Business. July, 2017.

About the author

Sherif Hany Mousa is a Technical Marketing Engineer with the Design to Silicon Division of Mentor, a Siemens Business, supporting Calibre physical and circuit verification products. He previously held positions as an analog quality assurance engineer and IC design consultant and has several publications in the field of analog layout porting. Sherif holds patents for an electrical-driven hotspot detection and correction flow, and advanced context-aware flow integrations. He has an MSc in Electrical and Communication Engineering.