March 3, 2022

Because of the high analog content in memory designs, designers must understand how various effects impact reliability and performance.

May 3, 2021

Learn how power-intent, LDEs, ESD and voltage-aware spacing techniques can particularly benefit from the use of static verification checks.

April 15, 2019

CAA is a valuable tool available to both design engineers and foundries to help them avoid layout-dependent effects during manufacturing.

July 20, 2015

In sessions at the 2015 Design Automation Conference, engineers who had worked on finFET-oriented projects revealed how the technology has changed their design practices and where others may want to think twice about making the move.

May 19, 2014

The 14nm and 16nm processes cover a range of technologies and are designed to succeed the 20nm generation. They bring with them a number of design challenges.

October 8, 2013

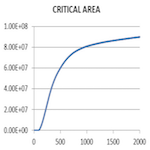

Electrically aware layout tools provide a more efficient alternative to time-consuming rip-up-and-retry practices in mixed-signal nanometer IC design.

October 2, 2013

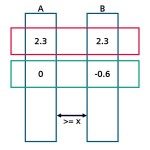

New layout-dependent effects (LDEs) arise at each process node. This methodology updates LDE parameters and uses on-the-fly simulation for early detection.

April 22, 2013

The arrival of the 20nm and finFET-based 14nm and 16nm processes bring with them challenges for custom IC design. These are the five key areas and a methodology that can address them.