February 8, 2024

Take a high level view of the AI strategies used within the Tessent family to improve across-the-board performance.

September 7, 2022

NVMe over Fabrics (NVMe-oF) extends the memory standard for burgeoning data traffic and the demands of AI and machine learning.

June 25, 2021

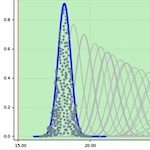

Learn how to bring together your NLDM and CCS models to reach timing closure faster with Solido Analytics.

March 22, 2021

SLS brings the power of product lifecycle management to the increasingly complex oversight challenges in electronic systems design.

March 1, 2021

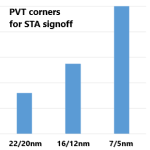

From 16nm, new complexities hinder .lib file characterization and verification but machine learning now offers an efficient way of managing them.

February 20, 2020

How can we refine our approach functional verification to deal with the increasing number of systems that leverage artificial intelligence.

September 13, 2019

SEMICON West showed a distinct thematic shift away from preserving Moore's Law to assessing the architectural implications of AI, as EDA was brought into the event.

August 9, 2019

Doc Formal rounds up some of the the key observations about verfication made during July’s Synopsys VC Formal SIG event in India.

March 13, 2019

Machine learning techniques help ensure the validity of Liberty Variation Format information for OCV analysis at lower process nodes.

January 28, 2019

The second part of this feature looks at how Wave Computing's objectives with its dataflow processing unit for AI mapped to the use of emulation in its development.