December 23, 2022

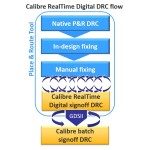

Automating reliability verification with tools that offer packaged checks provides greater consistency and accuracy across an increasingly complex process.

March 3, 2022

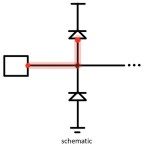

Because of the high analog content in memory designs, designers must understand how various effects impact reliability and performance.

January 13, 2022

More optimistic about the semiconductor industries prospects than for some time, Siemens Joe Sawicki identified key EDA challenges at DAC.

October 16, 2020

Reliability rule checks need - and now get - more granular analysis that allows designers to adopt proposed waivers with much greater confidence.

March 30, 2020

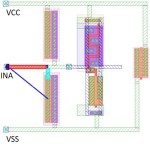

ESD has always been a major issue but with increasing densities and growing die sizes it is becoming a higher order concern. Automation and vizualization can help manage the task.

March 17, 2020

The RF and AMS specialist turned to design software that allowed it to run design checks during place and route.

February 14, 2020

P2P (point-to-point) resistance is fundamental to IC reliability verification. Handle it more efficiently with detailed, automated path layout analysis.

October 9, 2019

Learn how XML-based constraints can standardize rule development and use with coding examples for the Calibre PERC reliability platform.

July 16, 2019

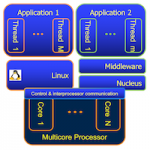

Embedded multicore systems require engineers to make choices around the hardware and software architectures, approaches to certification and more. This is a guide to the trade-offs involved and how to best leverage your options.

July 4, 2019

Doc Formal describes a strategy developed by his company Axiomise to apply formal verification proofs to open-source processor for safety, security and reliability.