September 13, 2021

Delivering physical implementations at new process nodes is getting ever harder. Learn how to stay on track by checking work is rule-compliant as you go.

July 20, 2021

How to carry out a sensible analysis of cloud EDA's potential, so you get the right tools and computational resources to deliver increasingly complex designs.

May 31, 2021

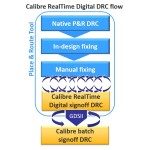

Using on-demand rule checks during place-and-route boosts efficiency and design quality.

October 16, 2020

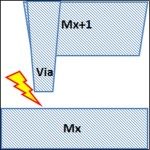

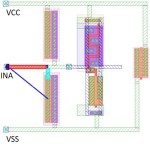

Reliability rule checks need - and now get - more granular analysis that allows designers to adopt proposed waivers with much greater confidence.

August 14, 2020

For physical verification and beyond, each process node requires new thinking, new tools and greater performance.

June 9, 2020

A collaboration between GlobalFoundries and Mentor has resulted in an innovative in-design fixing strategy across markets such as IoT, mobile, RF, graphics and networking.

May 26, 2020

A Mentor-Microsoft-AMD pathfinder demonstrates the potential benefits of cloud-based physical verification.

May 7, 2020

This case study shows how rising CMP simulation quality can be leveraged to detect the position and type of planarity hotspots before manufacture and verify the planarity of a layout.

March 30, 2020

ESD has always been a major issue but with increasing densities and growing die sizes it is becoming a higher order concern. Automation and vizualization can help manage the task.

March 17, 2020

The RF and AMS specialist turned to design software that allowed it to run design checks during place and route.