March 13, 2019

Machine learning techniques help ensure the validity of Liberty Variation Format information for OCV analysis at lower process nodes.

December 31, 2018

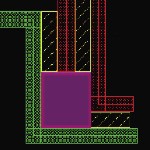

A detailed dive into how MBH strategies for litho hotspots have been enhanced to deal with double patterning at 20nm and below.

November 24, 2017

John Ferguson reviews the key capital metrics you need to review when deciding whether to move to a new process.

October 27, 2017

How to address increasingly complex patterning issues and debug them efficiently as design moves toward 12 and 10nm.

July 23, 2014

The 20nm node can offer power, performance and area advantages, but making these gains takes a deep understanding of the interactions between process and design.

January 13, 2014

A number of effects have led to a dramatic increase in interconnect resistance in the sub-32nm process nodes that demands the use of smarter routing.

October 8, 2013

Electrically aware layout tools provide a more efficient alternative to time-consuming rip-up-and-retry practices in mixed-signal nanometer IC design.

August 25, 2013

What ARM learnt when it ran a Mali GPU-based test chip through a Synopsys tool flow onto a TSMC 20nm process

April 22, 2013

The arrival of the 20nm and finFET-based 14nm and 16nm processes bring with them challenges for custom IC design. These are the five key areas and a methodology that can address them.

December 6, 2012

Using hierarchy and improved constraints management to accelerate static timing analysis at 20nm and below.