September 7, 2022

NVMe over Fabrics (NVMe-oF) extends the memory standard for burgeoning data traffic and the demands of AI and machine learning.

November 4, 2021

PIM memory boosts efficiency by operating on data without moving it to the CPU but realizing this type of novel technology posed power integration and planning challenges.

March 2, 2021

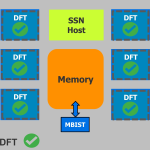

A new technique is especially efficient for AI chips with modular, tiled design strategies leveraging multiple instantiations of the same cores.

September 13, 2019

SEMICON West showed a distinct thematic shift away from preserving Moore's Law to assessing the architectural implications of AI, as EDA was brought into the event.

April 2, 2019

How Chips&Media used HLS on the development of a computer vision IP block.

March 26, 2019

The computational and algorithmic demands made by computer vision systems highlight HLS' value for AI system development.

January 28, 2019

The second part of this feature looks at how Wave Computing's objectives with its dataflow processing unit for AI mapped to the use of emulation in its development.

January 25, 2019

An increasing number of AI players are building their own silicon and finding that emulation is key to overcoming the major challenges.

May 4, 2018

Lauro Rizzatti gets a reality check on AI for both design tools and designs themselves from the formal verification specialist.

April 23, 2018

Artificial intelligence and machine learning require the performance and flexibility offered by embedded FPGA (eFPGA) technology.