May 31, 2021

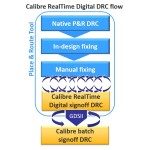

Using on-demand rule checks during place-and-route boosts efficiency and design quality.

March 17, 2020

The RF and AMS specialist turned to design software that allowed it to run design checks during place and route.

May 6, 2015

Using equivalence checking to validate ECOs in ARM core subsystem development at STMicroelectronics

March 27, 2014

Using a physically aware flow to ensure that fixing one ECO doesn't introduce another during sign off.

December 23, 2013

How Marvell used an enhanced ECO tool flow for SoC design to cut overall time-to-timing-closure by nearly 70%.