Reliability verification: It’s all about the baseline

How you can use the dedicated rule decks now being provided by foundries as the foundation for a reliability verification flow.

If you are an IC designer or verification engineer, you’re well-accustomed to using design rule checking (DRC), layout versus schematic (LVS), and parasitic extraction (PEX) rule decks provided by the foundry for automated verification. Using these decks just makes sense. They have been validated and qualified by the foundry. They leverage known good solutions for sign-off verification. Creating your own decks would have a tremendous cost in time and resources, with no guarantee the results would match your target foundry’s requirements.

Now there’s a new rule deck in town. The increased focus on reliability (both in performance and product lifetime) has broadened the need for context-aware reliability verification [1]. Foundries have responded by creating reliability rule decks. These deliver a wide range of reliability solutions, often starting with electrostatic discharge (ESD), latch-up (LUP), and interconnect reliability, but now including power management, electrical overstress (EOS), and other potential reliability impacts.

Foundry-qualified reliability rule decks make an excellent starting point for your reliability verification flows, and should be considered your baseline for them. EDA companies are providing verification tools that use these decks to automate and standardize the reliability verification process. And if you still need another reason, consider this: As reliability verification needs expand across the industry, customer demands are driving adherence to new and augmented reliability rules developed and qualified by foundries. They save design companies countless hours and resources that would otherwise be spent creating custom rule decks.

Foundry support for reliability verification

Taiwan Semiconductor Manufacturing Company (TSMC) was one of the first foundries to provide reliability rule decks. Its current ESD/LUP kit provides reliability verification for topology, point-to-point (P2P) resistance, current density (CD), and layout-based LUP rules [2]. As part of their TSMC9000 IP quality program – which has been designed to help customers improve intellectual property (IP) dependability – these rules help establish a consistent baseline for both design companies and IP providers across this ecosystem [3].

TowerJazz was the first commercial foundry to incorporate RESCAR-developed reliability checks into its standard reliability design kit offering, in the form of automotive reliability check templates. These checks enable designers to address the enhanced level of reliability compliance that standards, such as the functional safety standard ISO 26262, require from the entire automotive supply chain. Even though these reliability checks are targeted towards the analog portion of an SoC, they can be used to analyze and enhance the design’s overall reliability [4].

Design companies must be aware that each foundry’s offerings typically have a different reliability focus. ESD protection is a common thread but they diverge in other areas. For example, TSMC focuses on ESD, interconnect reliability, and LUP, at the IP and full-chip levels. The TowerJazz process design kit (PDK) supports checks for power management, ESD, and charge device model (CDM) protection, as well as a suite of analog design constraint checks that incorporate sensitive layout requirements, such as device alignment, symmetry, orientation/parameter matching, and more.

Establishing your reliability verification baseline

Most internal design and CAD support resources leverage the work of the foundries when creating or customizing rule decks for internal use. For DRC, LVS, and PEX rules, this means starting with the foundry-provided decks and applying relatively small additions and modifications as needed so that unique or proprietary verification requirements are satisfied. This is both more efficient in terms of time and resources, and ensures consistency across designs and nodes because the process always starts with the foundry rule deck as the source.

In the same way, companies should implement foundry-supplied reliability rule decks into verification flows with the assurance that their contents and requirements have been thoroughly vetted. From IP to full-chip reliability applications, the value of establishing a baseline for reliability acceptance throughout the design flow has been established [5]. Whether you have not done formal reliability verification before, or already have a customized in-house reliability checking process, foundry reliability rule decks provide the same benefits as DRC, LVS, and PEX decks—uniform, qualified requirements and consistent foundry maintenance across all projects and process nodes.

Many companies adopting foundry-provided reliability design rules incrementally, often by first supplementing any internal methodologies and rule checks already in place. A typical evolutionary path will start small, gaining trust in the process and the results, then transition more of the design flow to foundry-provided reliability decks.

When design teams evaluate the usefulness of a foundry-led reliability solution, they first have to understand what is being verified by the appropriate rule deck. This is important because companies may be using different foundries for different projects. Understanding different but distinct areas of reliability concerns a particular foundry’s reliability rule deck addresses should be part of that decision as to who gets the work.

The initial step is as simple as downloading the foundry’s reliability rule deck for your current design process node, and reviewing the contents with your reliability/ESD team. Next, you need to understand how well these offerings align with your internal requirements, flows, and design practices, as well as the capabilities of the tools you are using for context-aware automated reliability verification. For example, the foundry-provided ESD/LUP rules are a great place to start for developing a reliability baseline, but depending on what your foundry provides, you may need to make these types of addition to your full-chip checklist:

- Validation that all IPs are correctly implemented

- Context/voltage-aware LUP protection verification [6]

- Interconnect robustness analysis

- Stacked devices analysis in the context of the whole chip

- Verification that the correct power ties are used in wells

Reliability checking often requires ‘context awareness’, or the ability to consider both geometrical and electrical information together to determine the correct implementation. If your verification tools cannot perform this combined analysis automatically, you may find yourself spending a lot of time trying to implement these checks through manual annotation and custom code. Adopting tools that provide automated context-aware checks can ensure fast, accurate reliability checking and debugging.

Also, given today’s M&A environment, project teams in a merging company often continue to develop new versions and incremental updates of chips using the same foundries employed for their original products. Faced with the time and expense of transferring to a new foundry, they adopt the adage of ‘If it isn’t broken, don’t fix it.’ Whatever the reason, when sending different projects to different foundries, you must make sure you have a clear understanding of the reliability checks each provides, and confirm they align with your own internal requirements.

Beyond providing new design opportunities, new process nodes present new learning experiences for designers as they seek to understand the nuances of the flow and the potential reliability concerns around new devices and interconnects. Design starts, particularly those on incoming process nodes, benefit greatly from leveraging foundry-provided rule decks, as many of the lessons learned and acquired knowledge from previous nodes and foundries may not translate across.

Using a foundry reliability rule deck

IP validation—early and often

While full-chip sign-off is necessary for the completion of any design, getting there can be greatly enhanced by the verification of standalone IP blocks and larger blocks during chip assembly. Foundry rule decks usually provide internal switches that allow designers to run either full-chip checks or IP-based and block-specific checks.

IP-based checks allow the verification process to begin while design teams are still implementing and assembling IPs from internal groups and/or 3rd party IP vendors. Just as ensuring the IP being delivered to a design meets the baseline criteria in foundry-provided DRC rule decks is a given, the same should be true for reliability checks. As with DRC, validating reliability at each level as you select and build up the design provides a deterministic path to success as you consider these design elements in the context of the whole chip.

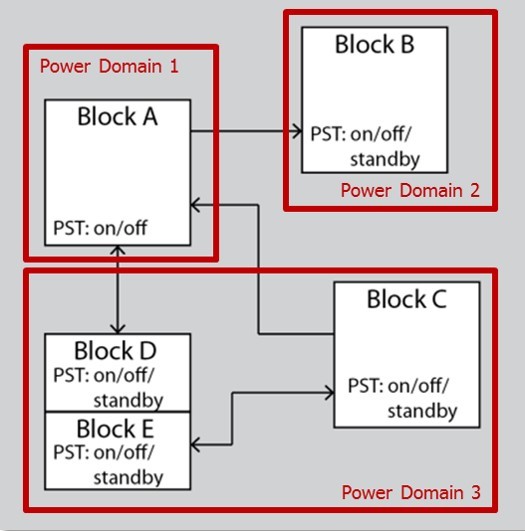

IP re-use, whether the blocks are developed internally or sourced externally, makes up a substantial portion of today’s designs. A significant challenge here lies is determining a block’s suitability and reliability for a new design. While the physical layout used in a previous design may remain unchanged, the reliability context of how that IP block is used in a new design must be validated. Figure 1 shows well-trusted IP placed in multiple power domains in a new design, with unified power format (UPF) power state tables (PST) controlling their activity. While each IP may work well in a standalone context or in their previous use, validation of how they all interact with (and are physically connected within) the new IC design as a whole must be rigorously performed, particularly when validating interactions between multiple power domains.

IP obtained from multiple sources is likely to contain different design styles and techniques. However, there are times where validation of consistent design styles and best practices can simplify long-term maintenance and reduce the cost of ownership. Identifying IP design differences early in the design process helps eliminate late-breaking issues during IP integration and assembly. For example, one design decision in which consistency is valuable across multiple IP is the choice of which common ESD techniques to use for I/O pin protection. Are all of your I/O IP blocks developed for distributed ESD protection (often common in ball grid array designs), or not?

Validation of existing IP becomes even harder when it also involves a process node or foundry change. Retargeting IP can be especially challenging when applying a process shrink, because special care must be taken with those parts of the design that should not shrink, such as interconnect robustness and device sizing for ESD protection. This is where foundry reliability rule decks are particularly helpful. While shrinking interconnect, transistor dimensions, and spacings across most of the design may be appropriate for the new node, maintaining correct geometrical dimensions where energy must be shunted (as is the case for ESD protection circuitry) is essential, and requires careful validation. Although new nodes may offer opportunities to improve device performance, they may also present new design considerations. For example, when transitioning from planar bulk transistors to FinFET or FD-SOI, designers must educate themselves on the differences in reliability characteristics between the old and new devices and processes.

Full-chip integration

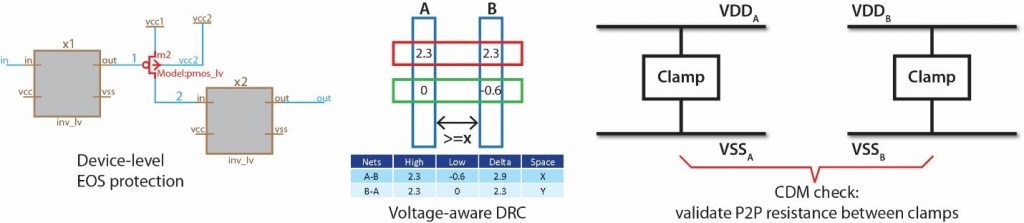

The verification of individual IP blocks is the foundation for verification of your chip assembly, but standalone IP verification lacks the overall context of how the blocks will be incorporated into the larger whole. Comprehensive reliability verification at the full-chip level is an equally important requirement. As shown in Figure 2, overall chip context is important when validating critical reliability applications, such as ESD and electrical overstress (EOS) protection, voltage-aware DRC (VA-DRC), and interconnect robustness (particularly critical for avoiding charge device model (CDM) issues by ensuring low resistance between ESD clamps).

Figure 2: Reliability applications necessary to verify critical reliability issues at the full-chip level (Mentor)

Some reliability checks must be performed both at the IP level and in the context of the full chip. Reliability rule decks used for both IP and full-chip runs often have settings or modes that define the verification level needed to generate the appropriate results. For device-level EOS, long-term reliability issues will arise if the bulk is tied to a higher voltage than the voltage at which the gate switches. This scenario creates gate-oxide stress that will cause failure over time. Such failures are hard to recognize because they are subtle design errors not easily identified in traditional SPICE simulations. To ensure that time-dependent dielectric breakdown (TDDB) does not lead to premature oxide breakdown of interconnect, VA-DRC spacing checks must be performed in a way that considers the voltages on these interconnects [7].

While most designers expect basic ESD checking from their automated tool flows, more complex reliability checks (e.g., interconnect robustness verification with point-to-point (P2P) and current density (CD) analysis) are also critical. CDM checking to protect gates that are directly connected to power/ground is required at advanced nodes because of the shrinking of gate oxide thickness and concerns across power domains. When active clamps are used, there is a need to validate resistance between global powers (of different domains) to avoid CDM issues.

Conclusion

For many IC design companies and IP suppliers, reliability verification is a new area, one with heightened visibility and different demands. Adoption of new process nodes affords a great opportunity for design companies to consider their entire ecosystem, from IP provider to final chip assembly. Foundry-qualified and foundry-maintained reliability rule decks enable design and IP companies alike to establish baseline robustness and reliability criteria without committing extensive time and resources to the creation and support of proprietary verification solutions. However, a thorough understanding of the coverage provided by a foundry’s reliability offering is essential to ensure that the baseline for your internal criteria is covered by each foundry’s rule deck, especially when multiple projects source different foundries. As with DRC and LVS rule decks, companies may need to work with their chosen foundries to expand rule deck coverage as new reliability needs arise.

Reliability verification tools provide a wide range of automated checking capabilities, and ensure consistent and accurate reliability checking based on a foundry rule deck. They are focused on finding and resolving reliability challenges from the block/IP level through full-chip sign-off verification.

Ensuring consistent, complete, and accurate reliability verification solutions is a critical step for ensuring long-term device performance and product lifetime. Starting with a foundry-qualified reliability rule deck provides a solid baseline and allows for future growth.

References

[1] Semiconductor Engineering. “Reliability Verification.” Last modified June 4, 2016. https://semiengineering.com/knowledge_centers/eda-design/verification/reliability-verification/

[2] Mentor Graphics Corporation. Mentor Graphics Calibre PERC Reliability Checking Solution Used for IP Quality Program by TSMC, Oct. 29, 2013.

https://www.mentor.com/company/news/mentor-tsmc-calibre-perc

[3] Taiwan Semiconductor Manufacturing Company. TSMC9000 Program.

http://www.tsmc.com/english/ dedicatedFoundry/services/tsmc9000.htm

[4] TowerJazz. Mentor and TowerJazz provide first commercial comprehensive suite of analog constraint checks for enhanced automotive reliability offering, Nov. 2, 2017. http://www.towerjazz.com/prs/2017/1102.html

[5] Hogan, Matthew. December, 2017. “Leveraging Baseline Checks for Robust Reliability Verification” Mentor, a Siemens Business.

[6] Hogan, Matthew. June 2017. “Automated and Context-Aware Latch-Up Checking with the Calibre PERC Reliability Platform” Mentor, a Siemens Business.

[7] M. Hogan, S. Srinivasan, D. Medhat, Z. Lu and M. Hofmann, “Using static voltage analysis and voltage-aware DRC to identify EOS and oxide breakdown reliability issues,” 2013 35th Electrical Overstress/Electrostatic Discharge Symposium, Las Vegas, NV, 2013, pp. 1-6.http://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=6635948&isnumber=6635896

Author

Matthew Hogan is a Product Marketing Director for Calibre Design Solutions at Mentor, a Siemens Business. He has more than two decades of design, field and product development experience. Matthew is an active member of the International Integrated Reliability Workshop (IIRW), is on the Board of Directors for the ESD Association (ESDA), contributes to multiple working groups for the ESDA and is a past general chair of the International Electrostatic Discharge Workshop (IEW). Matthew is also a Senior Member of IEEE, and a member of ACM. He holds a B. Eng. from the Royal Melbourne Institute of Technology, and an MBA from Marylhurst University.