October 19, 2023

Standard physical verification (PV) check reviews within EDA tools can reduce time-to-tapeout and mitigate risk.

September 3, 2021

SiP promises advances in transmission speeds, bandwidth, accuracy and low power but verification requires careful evolution of existing tools.

September 21, 2020

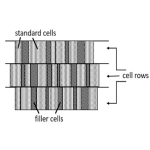

A physical verification-ready flow can speed project delivery by making your use of filler cells more efficient.

May 26, 2020

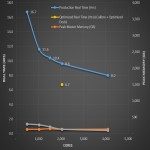

A Mentor-Microsoft-AMD pathfinder demonstrates the potential benefits of cloud-based physical verification.

March 9, 2018

Still using custom layout or place and route tools here? Ditch that time-consuming practice for a real database merge flow.

January 15, 2018

How to get the best PV results by reducing computational demands; handling data more efficiently and exploiting parallelization.

September 14, 2017

An alphabet soup of AI, HPC, 5G and the IoT has finally seeded creation of a design infrastructure for silicon photonics.

September 10, 2014

Innovation in physical verification is driven by incoming nodes but new tools and features can and should be fed back up the technology chain.

July 9, 2014

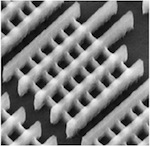

A change in the way the core compact models are developed has accelerated their development and, for the first time, allowed the models to be used not just for circuit simulation but to help guide process evolution as chipmakers play not only with materials but the shape of finFETs.

May 2, 2013

A look at some of the design and physical verification challenges of working with finFET and FD-SOI devices, including their impact on layout, DRC and LVS.