January 27, 2022

The strategy of designing for best power rather than for best timing in place-and-route delivers better results all around.

September 13, 2021

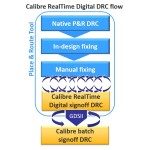

Delivering physical implementations at new process nodes is getting ever harder. Learn how to stay on track by checking work is rule-compliant as you go.

May 31, 2021

Using on-demand rule checks during place-and-route boosts efficiency and design quality.

September 21, 2020

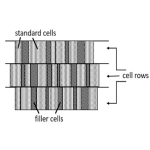

A physical verification-ready flow can speed project delivery by making your use of filler cells more efficient.

June 9, 2020

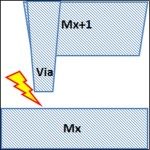

A collaboration between GlobalFoundries and Mentor has resulted in an innovative in-design fixing strategy across markets such as IoT, mobile, RF, graphics and networking.

March 17, 2020

The RF and AMS specialist turned to design software that allowed it to run design checks during place and route.

January 25, 2019

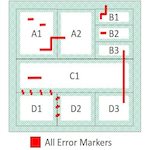

In a continuous-build design flow, at which level should your error markers be addressed?

March 9, 2018

Still using custom layout or place and route tools here? Ditch that time-consuming practice for a real database merge flow.

October 3, 2016

Multi-patterning, finFETs and more are forcing more detailed overhauls of P&R software at each process node. We dig into some of the key new issues and how they are being addressed.

October 18, 2014

Soft blocking to prevent cell spreading and other placement-optimization techniques helped improve power and clock speed on a Cortex-M7 test chip designed by ARM and Cadence.