April 3, 2024

A comprehensive guide to parasitics, how to perform parasitic extraction and the latest technologies available for this critical task.

October 19, 2023

Standard physical verification (PV) check reviews within EDA tools can reduce time-to-tapeout and mitigate risk.

August 8, 2023

We have the technology. Learn how to 'shift left' with Calibre DesignEnhancer and meet IR, EM and PPA objectives.

May 16, 2023

You must understand six comparison concerns and their effect on database equivalency. Adopt a solution with an in-depth object-based approach.

January 26, 2023

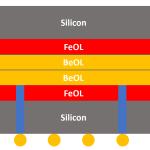

Learn more about the five interconnected workflows that are democratizing next generation design in the emerging chiplet age.

October 6, 2022

3D-IC presents major connectivity challenges in maintaining a golden netlist and managing necessary exceptions. Learn how to manage them.

May 10, 2022

Coordinate-based checking provides a streamlined way to verify designs around ESD before full-chip runs without the need for custom checks.

April 28, 2022

What are the options and how do you balance overarching CAD requirements and personal preferences?

January 13, 2022

More optimistic about the semiconductor industries prospects than for some time, Siemens Joe Sawicki identified key EDA challenges at DAC.

November 12, 2021

Pre- and post-processing EDA techniques help streamline design rule checks and delivery efficient waivers to speed design and debug.