January 13, 2022

More optimistic about the semiconductor industries prospects than for some time, Siemens Joe Sawicki identified key EDA challenges at DAC.

April 2, 2019

How Chips&Media used HLS on the development of a computer vision IP block.

March 26, 2019

The computational and algorithmic demands made by computer vision systems highlight HLS' value for AI system development.

June 1, 2016

By taking a pragmatic approach, the two technology giants have comfortably adopted high-level synthesis and verification - and have shared their experiences.

January 8, 2016

2016 marks the 20th anniversary of the term Electronic System Level (ESL), introduced by Gary Smith in 1996. Where are we now? And how will developments this year push the frontiers of practical ESL design?

September 24, 2015

High-level synthesis provides a way to explore hardware architectures to come up with the most efficient implementation for a given situation. But it has taken time for verification techniques to catch up with the idea and ensure design and architecture match.

December 16, 2013

Continuing our series on high-level synthesis (HLS) for low power design. Part Two details how HLS helps you make and evaluate architectural decisions.

October 21, 2013

Going inside HLS' basics shows how it can deliver power savings over 50% for some applications.

October 25, 2012

How Xilinx' Vivado HLS enabled the creation of an in-fabric, processor-free UDP network packet engine

March 7, 2012

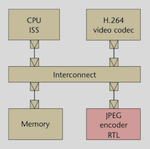

An evolved ESL-to-RTL methodology flow addresses the ‘discipline gaps’ between software and hardware engineering by using three system level-based software-hardware verification steps. The strategy is already available in TSMC’s Reference Flow 12.