June 25, 2021

Learn how to bring together your NLDM and CCS models to reach timing closure faster with Solido Analytics.

June 21, 2021

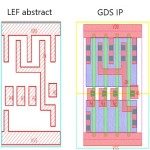

Overcome problems created by mismatches between library exchange format (LEF) and GDS or OASIS representations to avoid design delays.

May 31, 2021

Using on-demand rule checks during place-and-route boosts efficiency and design quality.

May 28, 2021

How to unify your design team to defeat the dark side of board systems design.

May 3, 2021

Learn how power-intent, LDEs, ESD and voltage-aware spacing techniques can particularly benefit from the use of static verification checks.

April 9, 2021

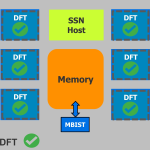

The best paper winner at DVCon 2021 details a comprehensive methodology for making the best use of formal verification for bug hunting

April 6, 2021

Joe Sawicki of Siemens EDA recently addressed the main trends in design delivery from architecture to validation to digital twins - and where they may soon take the industry and its products.

March 22, 2021

SLS brings the power of product lifecycle management to the increasingly complex oversight challenges in electronic systems design.

March 2, 2021

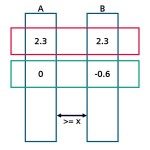

A new technique is especially efficient for AI chips with modular, tiled design strategies leveraging multiple instantiations of the same cores.

March 1, 2021

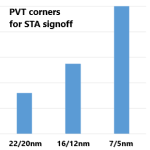

From 16nm, new complexities hinder .lib file characterization and verification but machine learning now offers an efficient way of managing them.