Use machine learning and visualization to accelerate Liberty file verification

As process technologies shrink and design complexity grows, design teams face increasing challenges in reaching timing closure for projects that depend heavily on the accuracy of Liberty models. At nodes above 90nm, non-linear delay models (NLDM) were chiefly used to abstract delays and transition times of cells at various points in the digital design flow. However, for smaller nodes, deep-submicron effects have come to the fore. These include temperature inversion, the Miller effect, dynamic IR drop, and high impedance for interconnects. NLDM models fail to account for these effects, making them less accurate for timing usage in newer technologies.

To address these accuracy challenges, composite current source (CCS) models have been developed. These are characterized much like NLDM models but can address the deep-submicron effects effectively.

NLDM and CCS challenges

CCS timing libraries typically include both CCS and NLDM models for each cell in the Liberty file and this gives the user flexibility. During synthesis and before place and route (P&R), there is no information available for interconnect parasitics. So, the timing engine of a synthesis tool will rely on the Wire Load Models in the Liberty files to estimate net parasitics based on fanout. Therefore, designers choose to use NLDM models to quickly iterate through their synthesis flow and generate a netlist that can then be passed though a P&R tool. At the implementation stage, when the design is fully routed and the parasitics information is available for all nets, more accurate CCS models are used to get timing as close to sign-off as possible.

Although minor differences between NLDM and CCS models are to be expected because they differ in their approaches to characterization, they should still correlate well with each other. Significant differences between them will lead to a discrepancies in the timing calculations during the implementation and sign-off stages.

To minimize the timing gap between various stages of a digital design flow, every effort should be made to ensure that the NLDM and CCS models are consistent for a given Liberty file. But given the huge sizes of the Liberty models, it is not only hard to compare the large amount of data involved using text editors, but also nearly impossible to debug any issues and resolve them in a timely manner. A lot of investment has therefore been made in the library verification tools since libraries form the heart of Static Timing Analysis. Traditional library verification tools perform textual parsing of these Liberty files in ASCII format for their completeness and correctness.

NLDM and CCS consistency checking

Solido Analytics is a machine-learning enabled library verification and debugging solution from Siemens EDA. It offers a complete range of rule-based checks supported by other library verification tools and much more within an information visualization-assisted debug and exploration environment. The tool undertakes a comprehensive validation of Liberty models and streamlines the process of debugging and fixing any errors in the files. These rule-based checks ensure the Liberty models are compliant and structurally-correct.

In addition to the built-in static rule-based checks set, Solido Analytics offers a custom rules API. This lets users add any new checks rules not already covered by the built-in set. For example, a simple check to find negative delays in the Liberty models can be easily written. Negative delays can exist in the libraries and mostly happen in very small FinFET cells when they are driving a very small load. Checks like these can be instantly added using the API.

The Solido Analytics dashboard provides real-time results in the form of waveform plots and data tables that show the same data in user-friendly ways and offers additional insights into the timing data. The tool supports comparison of all Liberty files (for all PVT corners) in the design or a select set of Liberty files.

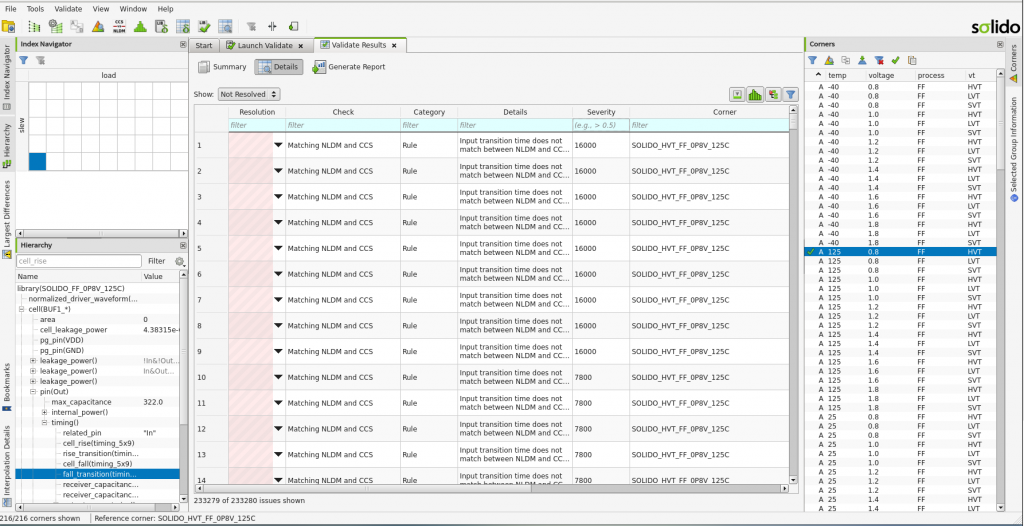

Figure 1 shows the tool initiating CCS vs NLDM consistency checks on loaded Liberty files in a dataset and displaying all the checks performed on it. The set of checks can be restricted to only failed CCS vs NLDM checks. Double clicking on the failure then highlights the corresponding corner in the corner pane on the right as well as the corresponding timing arc in the hierarchy pane.

A right-click on the timing arc lets users open the section of the data tables from the Liberty file where the problem exists. This is shown in a separate tab on the dashboard for further analysis (Figure 2).

Figure 2. Get easy access to a problem’s location in the Liberty file (Siemens EDA – click to enlarge)

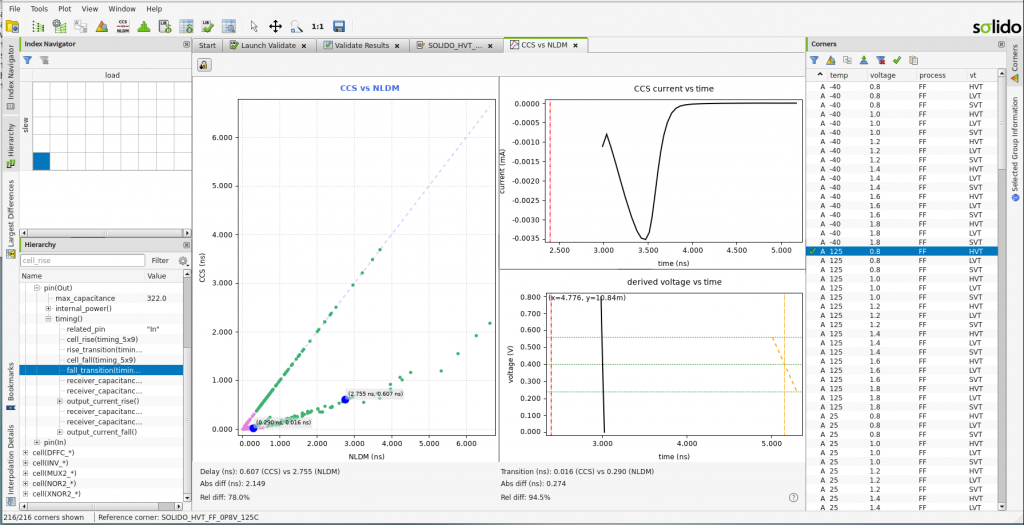

As an alternative, users can also display the CCS current waveforms and the corresponding voltage waveforms (calculated from the currents) in the advanced information GUI of Solido Analytics.

These waveforms compare the shape, delay and transition for that specific arc, slew and load across all PVTs in the dataset as shown in Figure 3.

The first plot (left) shows the CCS vs NLDM transition and delay comparison for a specific timing arc, slew and load (the current selection in the hierarchy dock on the left). Each point represents an individual PVT, with the delays and transitions colored separately (green for propagation delay and pink for transition time).

The line in the center is the ‘reference’ line. This represents a perfect match between the NLDM values (delay and transition) and the corresponding CCS values. Therefore, the points on the line have no errors and the NLDM and CCS values correlate well for them. Points not on the line indicate differences in the NLDM and CCS values and the magnitude of the differences depends on the distance between the point and the reference line.

The green points clustered together at the bottom of the plot have the largest number of differences between the NLDM and CCS values. All points on the plots are clickable and will generate the corresponding CCS and derived voltage waveforms to help debug issues.

This example shows how Solido Analytics helps identify and visualize a clear mismatch that must be fixed to reduce or, better yet, eliminate the delay calculation gap at the implementation and sign-off stages in the digital design flow.

Benefits

The interactive dashboard of Solido Analytics provides users a one-stop validation tool. The library visualizer interface offers flexibility to customize plots and compare multiple Liberty files in minutes. This gives users the information they need quickly, increases their understanding of the data in all the libraries in their dataset, and enables faster and more accurate decision-making. Furthermore, the single click Liberty file entry from the GUI takes users to the exact location of the problem and expedites debug.

Solido Analytics has over one hundred built in rule-based checks. These cover the rules most frequently used to verify a Liberty structure. Also, as noted, the user can instantly add custom checks using an API. This enables thorough validation of the Liberty files and gives design teams flexibility. They can create a validation deck that covers all of the scenarios they care about.

The tool can parse and analyze extremely large Liberty files of 10GB and above and is scalable to thousands of CPUs when needed. IP and design teams can therefore use it to open and view the contents of GB-sized Liberty files that text editors do not handle well, without experiencing slowdowns. This allows for much more efficient investigation or debugging sessions.

The CCS vs NLDM consistency check shown here is one of the many attractive features of the Solido Analytics tool that shortens the validation cycle and significantly reduces the engineering effort required to fully verify libraries. The tool has been designed to be powerful yet easy-to-use. Users do not have to be experts in library characterization – although library characterization teams will appreciate what the tool has to offer.

Conclusion

Accurate libraries are the foundations of successful design tape-outs. What today’s design teams need is a solution that lets them sift through huge amounts of data and debug any issues quickly and early, thus avoiding late-stage surprises.

Solido Analytics not only enables the users to traverse through the humongous Liberty files that are common in smaller technology nodes, but also displays information in a way that allows them to understand all the key data quickly and easily. The powerful yet easy-to-use tool allows not only the library characterization teams but also the design teams to verify the correctness of their Liberty files. Because of this, there has been steady growth in the usage of Solido Analytics. It is in use at leading foundries, IP providers, and semiconductor companies worldwide.

Tina Durgia is a Product Manager for AMS verification at Siemens EDA and is responsible for the Solido Characterization Suite. Tina holds a Master’s degree in Electrical Engineering from Santa Clara University and has more than 13 years of experience in EDA across various digital design products including static timing analysis, place and route, logic synthesis and power analysis.

Tina Durgia is a Product Manager for AMS verification at Siemens EDA and is responsible for the Solido Characterization Suite. Tina holds a Master’s degree in Electrical Engineering from Santa Clara University and has more than 13 years of experience in EDA across various digital design products including static timing analysis, place and route, logic synthesis and power analysis.