January 27, 2022

The strategy of designing for best power rather than for best timing in place-and-route delivers better results all around.

January 27, 2022

Generating accurate ASIL metrics early in the functional safety lifecycle, reduces time-to-certification for ISO26262.

January 13, 2022

More optimistic about the semiconductor industries prospects than for some time, Siemens Joe Sawicki identified key EDA challenges at DAC.

November 12, 2021

Pre- and post-processing EDA techniques help streamline design rule checks and delivery efficient waivers to speed design and debug.

November 4, 2021

PIM memory boosts efficiency by operating on data without moving it to the CPU but realizing this type of novel technology posed power integration and planning challenges.

October 21, 2021

Innovation is extending the technique's power across areas such as context-aware layout, accounting for multi-patterning and implementing fill.

September 13, 2021

Delivering physical implementations at new process nodes is getting ever harder. Learn how to stay on track by checking work is rule-compliant as you go.

June 21, 2021

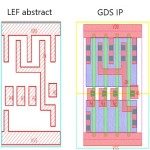

Overcome problems created by mismatches between library exchange format (LEF) and GDS or OASIS representations to avoid design delays.

May 31, 2021

Using on-demand rule checks during place-and-route boosts efficiency and design quality.

April 29, 2021

The best paper at DVCon Europe 2020 analyzed different multiclock strategies for SoCs for their power and flexibility