How UPMEM ensured effective power delivery for its processor-in-memory design

PIM memory boosts efficiency by operating on data without moving it to the CPU but realizing this type of novel technology posed power integration and planning challenges.

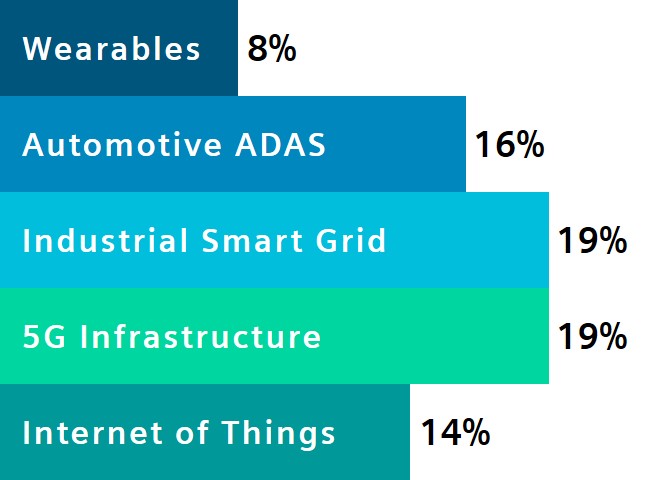

As applications around consumer wearables and Industry 4.0 grow at an astounding rate, the underlying analog and mixed-signal functionality needed to deliver them is accelerating in importance, size, and complexity. Many of today’s computing demands include wireless transmission, mobility, and sensors, combined with enough processing power and memory to acquire, manage, and manipulate a flood of data. This demand growth is driving a significant increase in design starts (Figure 1).

Figure 1. Emerging areas in semiconductor design are growing at well above the industry average (Semico)

To make these applications practical and profitable, one fabless semiconductor company is bringing innovative new technology to the IC industry. UPMEM, based on Grenoble, France, recognized that data movement in and out of memory is a dominant cost factor in IC operation. Data movement between the CPU and the DRAM modules uses 20X more energy than the CPU operations themselves. This creates serious efficiency issues for servers with data-intensive applications.

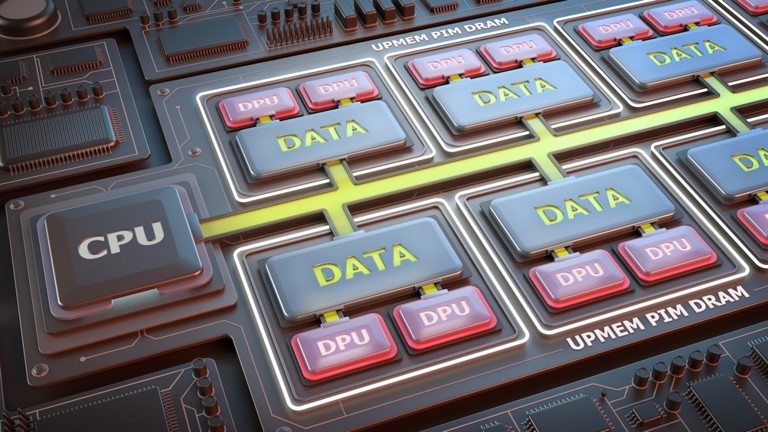

UPMEM’s solution? A processor-in-memory (PIM) DRAM module intended to replace traditional DRAM dual in-line memory modules (DIMMs). The UPMEM PIM-DRAM module can operate on data without moving it to the CPU (Tigure 2) and therefore offers new performance opportunities for a whole host of data-intensive applications. These include pattern matching, index database search, multi-criteria analytics, and image recognition.

Companies who replace DIMMs with PIM-DRAMs can thus speed up the performance of their products by up to 20X while simultaneously reducing power requirements by up to 13X. Needless to say, both changes can reduce the operating costs of the final product and enhance marketability.

However, because the PIM-DRAM development process was so different from the typical digital design process, UPMEM faced significant design and verification challenges. Incorporating standard cell-based digital design into a DRAM to create their PIM-DRAM IC meant UPMEM had to ensure the power delivery network was both adequately sized and optimized in a process where the routing has many times higher resistance than a typical digital process. They needed power analysis tools that could address multiple power analysis requirements, and power analysis technology that could verify combinations of functionality no one in the industry had encountered before. Unfortunately, they found that power planning and power integrity verification were two areas not well-served by available EDA tools and processes.

mPower power integrity analysis

While looking for alternative solutions, UPMEM was introduced to the mPower power integrity analysis toolsuite from Siemens EDA. The mPower power integrity solution held the promise of providing the performance and scalability its engineers needed to analyze the power implementation of their PIM-DRAM design accurately and efficiently. After implementation, UPMEM found that the mPower solution enabled its team to perform all the required power analysis within existing design flows.

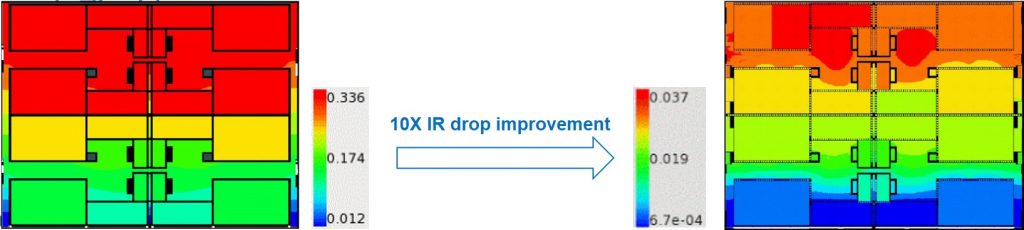

Power mesh optimization

Very limited and highly resistive routing resources in the PIM-DRAM design created a complex power mesh implementation. UPMEM combined IR measurements obtained using the mPower tool with place and route (P&R) iterations at the floorplanning level to optimize multiple areas in the design. Not only were the engineers able to iterate quickly through the floorplanning process, but the high precision results of the mPower analysis resulted in a 10X improvement in power distribution (Figure 3). Moreover, although this atypical process was highly resistive, and not optimized for standard P&R flows, UPMEM was able to perform all of the power analysis tasks easily and quickly within its standard design flows.

Figure 3. mPower power integrity analysis enabled UPMEM designers to optimize power during floorplanning.(Siemens EDA – click to enlarge)

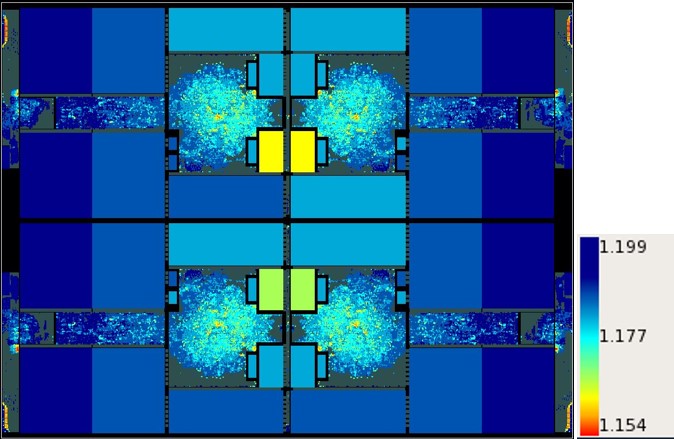

Post-implementation signoff

In addition to floorplanning optimization, UPMEM used the mPower Digital software for static and dynamic power analysis during post-implementation signoff. A full-chip power analysis typically ran in ~15 minutes, due to the scalability of the mPower software. This allowed the team to run multiple iterations per day (Figure 4).

Figure 4. UPMEM’s designers could complete multiple post-implementation power analysis runs per day on PIM-DRAM designs.

Ease of adoption and use

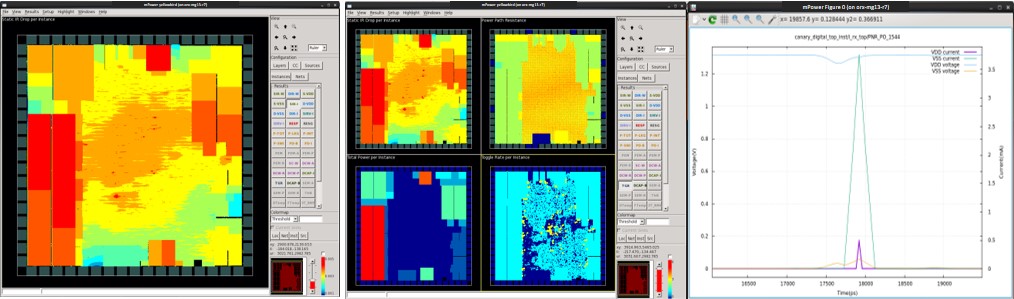

UPMEM was able to implement and apply mPower relatively easily, due in part to the use of non-proprietary industry-standard formats, as well as the ability to display results in all design tools. Ease of use was further enhanced by the fast, stable quad-view mPower GUI that supports mPower invocation and quick, accurate results debugging, while providing designers with a consistent and user-friendly interface (Figure 5).

Figure 5. The mPower GUI enabled UPMEM to easily integrate power analysis into its design flows and perform fast, efficient debugging (Siemens EDA – click to enlarge)

Summary

Because it offers full flexibility in data processing operations, with less complexity and at a relatively small implementation cost, UPMEM’s innovative PIM-DRAM module could be revolutionary for many design companies. The mPower power integrity solution gave UPMEM the performance and scalability they required to analyze power implementation from floorplanning through tapeout using both dynamic and static analysis. The ability to rigorously analyze both analog and digital implementations in the mPower integrated power analysis process provided UPMEM with the confidence that their new PIM-DRAM module would deliver the power, performance, and reliability as designed.

About the author

Joseph Davis is senior director of product management for Calibre interfaces and mPower power integrity analysis tools at Siemens Digital Industries Software, where he drives innovative new products to market. Prior to joining Siemens, Joseph managed yield simulation products and yield ramp projects at several leading semiconductor fabs, directing yield improvement engagements with customers around the world and implementing novel techniques for lowering the cost of new process technology development. Joseph earned his Ph.D. in Electrical and Computer Engineering from North Carolina State University.