September 19, 2019

Parasitic extraction has to take more account of inductive effects as operating frequencies rise and feature sizes shrink in complex SoCs.

September 13, 2019

SEMICON West showed a distinct thematic shift away from preserving Moore's Law to assessing the architectural implications of AI, as EDA was brought into the event.

September 10, 2019

The Portable Stimulus Standard helps overcome many of the verification challenges inherent in the strict requirements of ISO 26262.

September 9, 2019

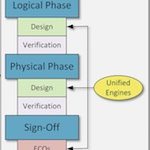

Complex SoCs need systemic optimisation to achieve best time to results, enabled by the use of a unified RTL-to-GDSII flow underpinned by a unified data model.

July 23, 2019

An IDE designed to catch typographical errors, missing declarations and inconsistent references in your code can hugely reduce your time in debug.

June 11, 2019

How to remove or extract portions of a layout for easier, more focused and faster project delivery.

May 15, 2019

Text editors have major debug limitations that the use of hyperlinks in integrated development environments help you overcome.

April 2, 2019

How Chips&Media used HLS on the development of a computer vision IP block.

March 26, 2019

The computational and algorithmic demands made by computer vision systems highlight HLS' value for AI system development.

January 28, 2019

The second part of this feature looks at how Wave Computing's objectives with its dataflow processing unit for AI mapped to the use of emulation in its development.