April 29, 2021

The best paper at DVCon Europe 2020 analyzed different multiclock strategies for SoCs for their power and flexibility

November 6, 2017

Sequential equivalence checking can be used to show that a block of sequential logic produces the same output for the same inputs after it has been modified by optimization techniques such as clock gating or register re-timing.

May 30, 2016

Sequential equivalence checking can help trap errors introduced by clock gate insertion, uninitialised registers, and X propagation issues.

May 31, 2015

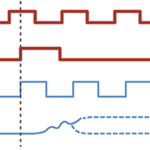

Complex processes and aggressive synthesis interventions are increasing the risks of metastability, creating a need for netlist-level CDC verification

May 30, 2015

Clock-tree generation is coming under increased scrutiny because of its role in dynamic power consumption and problems caused by on-chip PVT variation.

May 7, 2013

Better upfront analysis can help avoid propagating errors from RTL into the netlist, and reveal a number of ways to improve the quality of your final design.

April 9, 2013

The chipmaker used Calypto’s PowerPro to carry out power analysis of its latest core design at the RTL rather than at post-gate synthesis.

March 11, 2013

The multiple clock domains on today's SoCs create a hotbed for clock-domain crossing bugs to thrive. Low-power design techniques increase the complexity of tracking these bugs down. Find out how these failures arise and what to do about them.

August 23, 2012

The verification challenge is best addressed by a combination of highly targeted tools, according to Pranav Ashar, CTO of Real Intent.