December 23, 2022

Learn how UMVC helps bridge between SystemC and System Verilog using transaction level modeling for test and library efficiency.

January 12, 2022

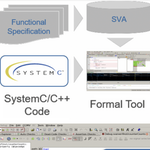

Automated formal technologies can be used to ease the debug and functional verification burden of SystemC/C++ code prior to high-level synthesis. This tutorial, first presented at DVCon Europe explores how these formal techniques can be deployed and provides real-world examples.

August 19, 2019

Refactoring saves time and resuources by converting code to a common format and eliminates redundancies to make it more readable and maintainable.

July 23, 2019

An IDE designed to catch typographical errors, missing declarations and inconsistent references in your code can hugely reduce your time in debug.

March 15, 2017

DVCon China general chair Andy Liu discusses Accellera’s new addition to its design and verification conference series (简体中文).

March 15, 2017

DVCon中国大会主席刘红亮讨论了Accellera新增的DVCon中国ASIC设计和验证会议的看点。

September 24, 2015

High-level synthesis provides a way to explore hardware architectures to come up with the most efficient implementation for a given situation. But it has taken time for verification techniques to catch up with the idea and ensure design and architecture match.

October 23, 2012

The FPGA vendor's new flagship is now on public release. It adds an array of features, including support for system-level to HDL synthesis.

May 23, 2012

VHDL is a hardware description language with rich constructs that can model complex systems. It can also be constrained for use as the starting point of an FPGA or ASIC design.

March 28, 2012

How SystemC enables system modelling at higher levels of abstraction, and the creation of virtual platforms.