March 21, 2022

Automating executable specifications as they evolve can deliver major efficiencies.

January 12, 2022

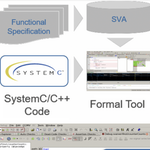

Automated formal technologies can be used to ease the debug and functional verification burden of SystemC/C++ code prior to high-level synthesis. This tutorial, first presented at DVCon Europe explores how these formal techniques can be deployed and provides real-world examples.

February 28, 2020

How the use of declarative, constraint-based descriptions can help you focus command sequences on areas of interest.

October 16, 2019

Power intent files have increased efficiency and the use of an IDE can prevent them becoming outdated as a design evolves.

September 25, 2019

An IDE is critical to top quality refactoring. Here are some tips and examples of how to achieve that.

August 19, 2019

Refactoring saves time and resuources by converting code to a common format and eliminates redundancies to make it more readable and maintainable.

July 23, 2019

An IDE designed to catch typographical errors, missing declarations and inconsistent references in your code can hugely reduce your time in debug.

August 31, 2017

Doc Formal concludes his introduction to formal verification with a practitioner's view of the technology.

July 25, 2017

This introduction to the new Accellera standard includes a demo of portable stimulus in use to fully verify a DMA engine.

March 15, 2017

DVCon China general chair Andy Liu discusses Accellera’s new addition to its design and verification conference series (简体中文).