How to achieve fast, automated, sign-off verification of DFM hotspot fixes in P&R

A collaboration between GlobalFoundries and Mentor has resulted in an innovative in-design fixing strategy across markets such as IoT, mobile, RF, graphics and networking.

Internet of Things (IoT), mainstream and high-end mobile, radio frequency (RF), graphics, networking, and power-efficient system-on-chips (SoCs) – the advanced technology nodes used for these designs include complex and design-sensitive fabrication processes. To achieve maximum yield while also ensuring their designs meet the intended performance, IC designers must look beyond design rule checking (DRC) compliance to design for manufacturing (DFM) optimization.

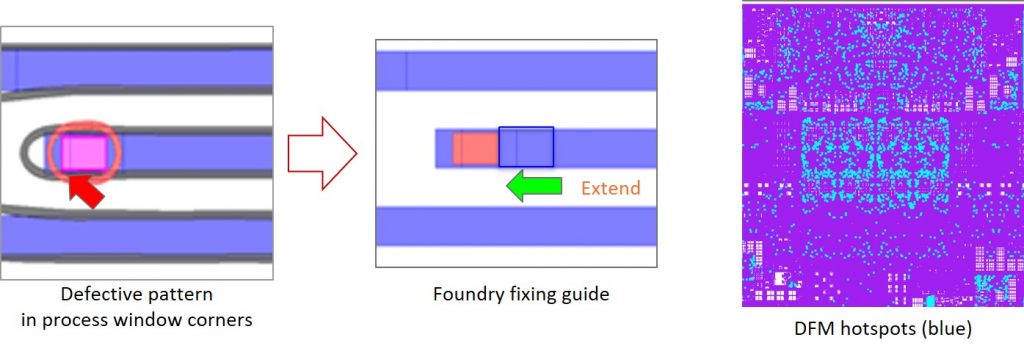

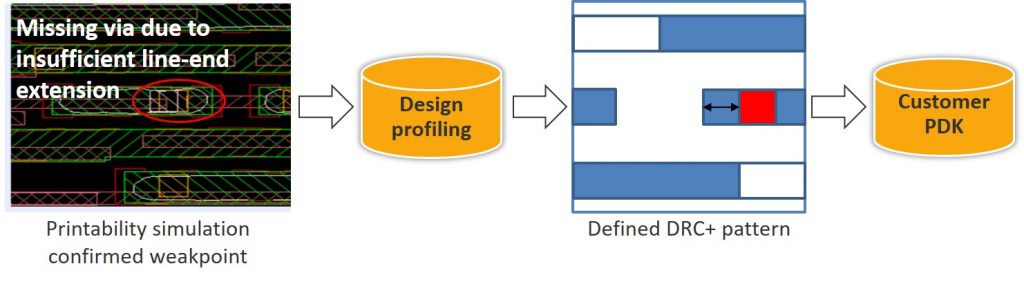

DFM techniques have been around for quite a while and have, in one form or another, made their way into nearly every verification flow. For example, DRC+, pioneered by GlobalFoundries, is a signoff DFM tool that combines the Calibre Pattern Matching tool with a proprietary library of yield detractor patterns to detect defective patterns (hotspots) in the layout that may lead to manufacturing defects. Design engineers must either fix these hotspots or minimize their total number before tape-out. Figure 1 shows a potential hotspot (here a via open), and how it appears as a hotspot pattern.

Figure 1. A potential manufacturing hotspot and its corresponding design pattern (GlobalFoundries/Mentor)

While foundry guidelines enable designers to fix these types of hotspots quickly and accurately, a typical design can contain thousands of such hotspots (Figure 2). Fixing these manually outside the place and route (P&R) process is time-consuming and iterative. Designers must iterate DRC after every round of fixes. In addition, these fixes may impact design timing and this may require even more changes.

Not surprisingly, IC design companies prefer an automated EDA process that helps them quickly find and fix these hotspots during design implementation. This articles describes how GlobalFoundries and Mentor, a Siemens Business, created an automated flow that not only supports in-design identification and fixing of DFM hotspots, but also provides Calibre signoff-quality DRC verification of the applied fixes.

Automated hotspot detection, correction and verification in P&R

DFM kits

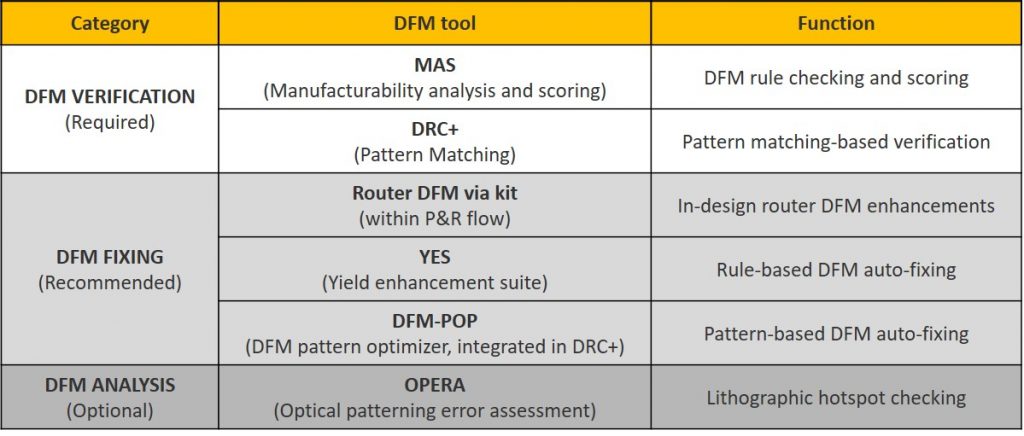

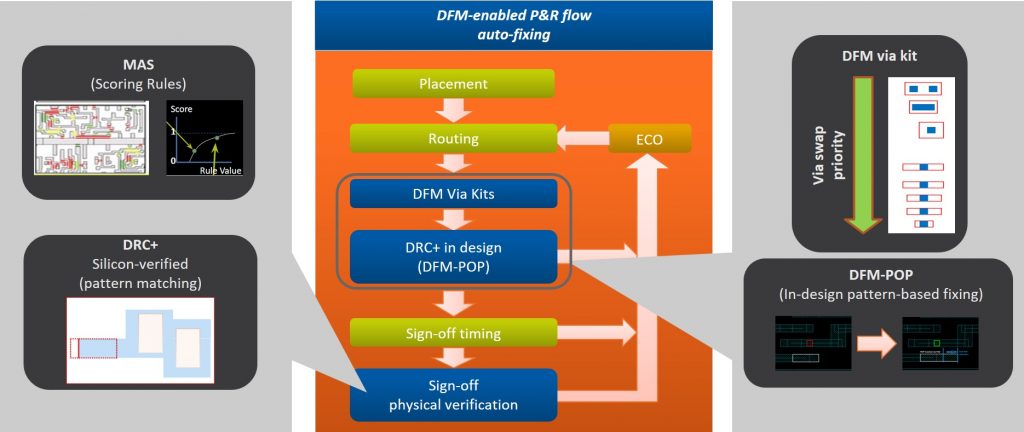

To support in-design hotspot resolution flows, GlobalFoundries developed DFM kits that designers can use as part of a seamless implementation flow to run exhaustive physical signoff runs and fix any hotspot issues. These toolkits cover three major DFM functionalities (Figure 3):

- DFM verification

- DFM fixing

- DFM analysis

These DFM functions are enabled during P&R, allowing designers to quickly detect, fix, and check hotspot issues during implementation (Figure 4).

Figure 4. The GlobalFoundries DFM flows in P&R allow designers to quickly detect and fix potential issues (GlobalFoundries/Mentor – click to enlarge).

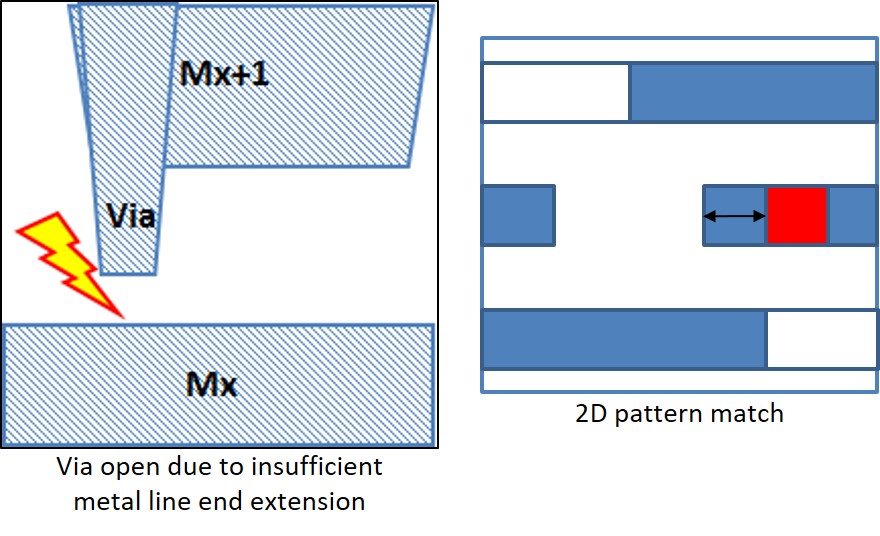

Hotspot pattern analysis

The first step in any DFM hotspot flow is to detect those on the design. The GlobalFoundries DRC+ pattern matching tool uses the Calibre Pattern Matching engine to detect defective patterns on the design. However, before you can detect a hotspot, you must know what it looks like. Sources of hotspot patterns include foundry data, such as a defect scan, printability simulation, or a physical failure analysis. GlobalFoundries identifies defective patterns by profiling the design, and then provides pattern definitions in the DRC+ libraries sent to customers as part of a PDK release.

For example, the hotspot shown in Figure 5 is from a printability simulation run, which exposes a missing via due to an insufficient line-end extension. After design profiling, a DRC+ pattern is defined for this hotspot and included in a PDK.

Figure 5. Design profiling is used to locate and convert potential hotspots into DRC+ patterns for inclusion in the PDK (GlobalFoundries/Mentor – click to enlarge)

Hotspot fixing

Once this hotspot pattern library is created, design teams can use the DRC+ process in the PDK with the Calibre Pattern Matching tool to find known hotspots in their layouts during design implementation. Designers can choose between three fixing techniques with the GlobalFoundries DFM toolkit.

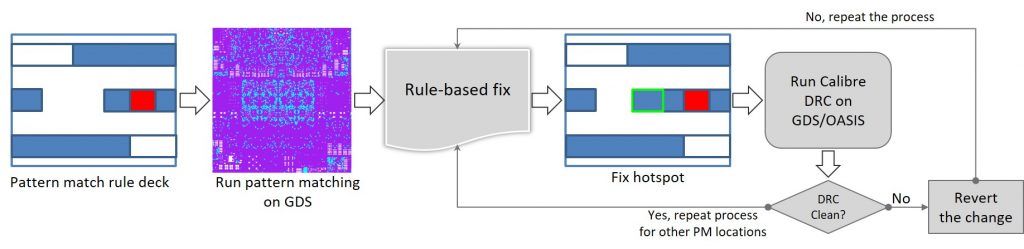

Rule-based automated fixing

The Yield Enhancement Suite (YES) method fixes hotspots using a rule-based process outside the P&R flow. Designers start with a rule deck that checks for DFM opportunities, including DFM hotspots, and then applies rule-based fixing automatically. Every time a fix is applied, Calibre DRC is run to ensure that the areas where fixes were made are DRC clean. If the areas are DRC-clean, the process leaves the change in place and moves on to the next hotspot location. If not, the change is reverted to the original layout before the process continues to the next location. Figure 6 shows the YES fixing flow.

The advantage of the YES flow is a higher fixing rate because various fixes are applied in an iterative fashion and the iterations continue until the fixes are Calibre DRC-clean. However, there are two distinct disadvantages. Because this process takes place outside the P&R flow, any timing impacts caused by the fixes are not addressed. This omission can result in cases where the hotspots are fixed but design timing is not satisfied. Also, running incremental Calibre DRC verification on the windows in which the fixes are made is difficult and time-consuming. It requires extra setup specifications to stream out partial GDSII from the layout and, more important, to filter out any false DRC errors caused by running on partial data — an often tricky and complicated undertaking.

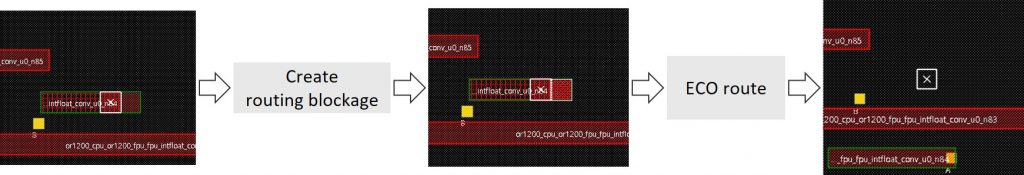

In-design fixing with rip and reroute

An alternative fixing method uses an in-design engineering change order (ECO) approach where the router performs a local rip-up and re-route of the layout (Figure 7). Patterns representing the hotspots are converted into routing blockages, which the router honors when it performs the ECO re-route. The router automatically checks for any DRC violations using its internal DRC engine (not a signoff Calibre DRC engine).

Figure 7. The ECO approach requires the router to re-route the layout to avoid creating the hotspots (GlobalFoundries/Mentor – click to enlarge)

The advantage of the ECO flow is that the fixing occurs within the P&R flow, so both the DRC correction and any timing impact of the fixes is verified. However, some of the fixes may not be signoff-clean because the DRC verification is done using the P&R tool’s internal DRC engine. In addition, the ECO approach requires a local rip-up and re-route of the design, which is typically time-consuming. Worse, it can create new hotspots and new timing impacts which then require further correction.

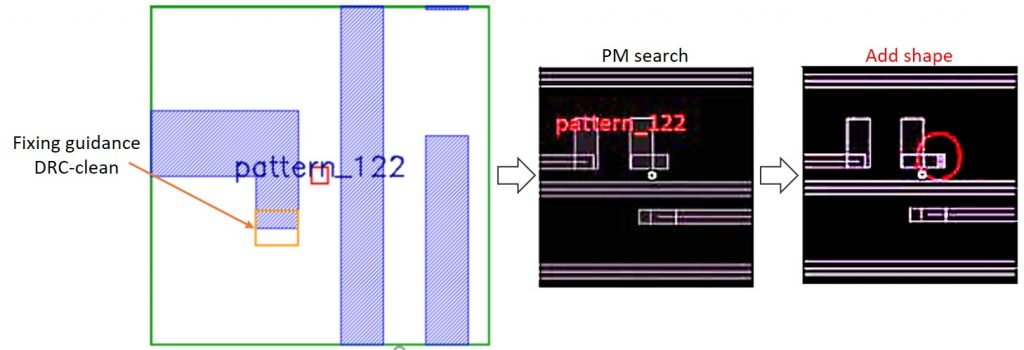

Pattern matching-based fixing

The third fixing option uses a pattern matching process. The DFM pattern optimizer (DFM-POP) approach is also an in-design method, but one that takes advantage of the DRC+ kit. The DFM-POP method is used for fixing pattern matching violations with the router, but it only requires changes to a minimal part of the design rather than a local rip-up and re-route (Figure 8). Both the hotspot patterns to check for and their suggested fixes are defined in the Calibre Pattern Matching rule deck. The Calibre Pattern Matching process is run on the entire design to find the hotspots and attempt fixes.

Figure 8. DFM-POP uses the DRC+ pattern matching technology to find and fix hotspots during place and route (GlobalFoundries)

Because this approach imposes minimal routing changes, there is a negligible impact on timing. Fixes are still verified using the P&R tool’s internal DRC engine, rather than the Calibre sign-off engine, so some errors may remain. Moreover, fixing all hotspots by re-routing is not possible, due to the complexity involved in fixing these hotspots.

Now, consider a fourth option.

Pattern matching-based fixing with signoff DRC verification

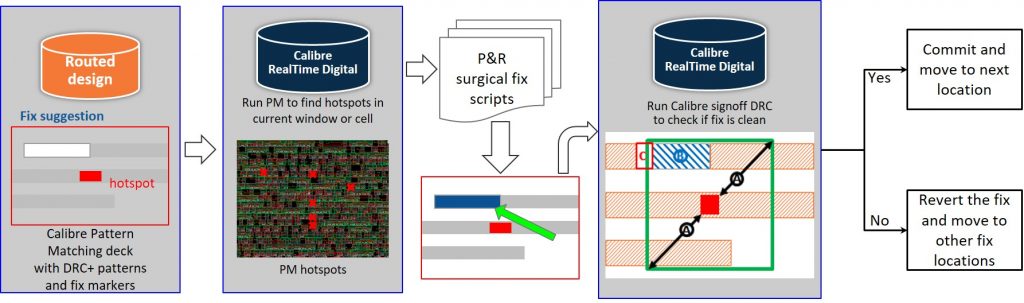

GlobalFoundries and Mentor have devised a way to optimize the DFM-POP fixing method that adds Calibre signoff-quality DRC checking inside the P&R process. GlobalFoundries created P&R scripts that invoke the Calibre RealTime Digital tool (using the Calibre DRC sign-off engine) to check the regions where fixes are attempted (Figure 9). These P&R ‘surgical’ fix scripts are run on the areas where hotspots are identified. Immediately after each fix, the script invokes the Calibre RealTime Digital API to perform Calibre signoff-quality DRC checking only in the area where the fix was attempted. If the Calibre RealTime Digital feedback returns no errors, then the fix is committed and the focus moves to the next hotspot location. If the fix generates a sign-off DRC error, then the fix is reverted and attempted on the next location containing the same type of hotspot.

Figure 9. Optimized DFM-POP fixing adds Calibre DRC sign-off quality checking using the Calibre RealTime Digital interface (GlobalFoundries/Mentor – click to enlarge)

This optimized DFM-POP flow enables designers to fix their hotspots surgically with Calibre signoff-quality DRC feedback while maintaining timing constraint compliance. By eliminating the need to iteratively stream out the entire GDSII database and run Calibre sign-off DRC on an entire block until the block is DRC clean, the optimized DFM-POP flow can accelerate DRC closure and reduce the time for tapeout by weeks.

Conclusion

Locating and fixing DFM hotspots during design implementation is a challenging and time-consuming task, albeit one that has become essential given today’s complex manufacturing processes. Facing market and resource constraints, design companies look to their EDA toolset for automated support for such processes. Foundries and EDA companies often work together to provide such solutions.

GlobalFoundries has pioneered an automated in-design fixing flow to identify and fix hotspots in their 22FDX DRC+ and DFM-POP flows. It uses the Calibre Pattern Matching tool to create a library of hotspots. This library is then employed to find occurrences of these patterns in a design layout. Once hotspots are identified in a design, designers run foundry-provided surgical fixing scripts in P&R to fix the hotspots, with signoff-quality DRC verification provided by the Calibre RealTime Digital API. Because both the fixes and DRC checking are done in a surgical fashion, the time needed to fix these hotspots is significantly reduced.

Collaborations such as these provide mutual benefit for everyone concerned. Foundries can be assured that submitted designs have been strengthened against manufacturing variation, while design companies can accelerate signoff DRC closure for their designs, potentially reducing tapeout time by weeks, while providing assurance that their designs will achieve their yield and performance targets.

About the authors

Uwe Paul Schroeder is a deputy director of design enablement at GlobalFoundries. He is responsible for leading design for manufacturing teams working on yield and design optimization for advanced technologies, and ensuring scalability of new technology nodes. He received his diploma in chemistry from Technische Universität Clausthal, and a Ph.D. in chemistry from the University of Stuttgart. Uwe can be reached at email uweDOTschroederATglobalfoundriesDOTcom

Janam Bakshi is a senior design enablement engineer at GlobalFoundries. He focusing on using silicon learning to develop DFM decks that improve yield and reduce systematic defects. He holds a B.Eng. in electronics and communication engineering from Gujarat Technological University, and a M.Eng. in electrical and electronics engineering from the California State University at Sacramento. Janam can be reached at email janamDOTbakshiATglobalfoundriesDOTcom

Srinivas Velivala is a product manager in the Design to Silicon division of Mentor, a Siemens business. He is responsible for developing the Calibre RealTime interface and other Calibre integration and interface technologies. Before joining Mentor, he designed high-density SRAM compilers. In addition to his more than 12 years of design and product marketing experience, Srinivas holds a B.S. and M.S. in Electrical and Computer Engineering. He can be reached at srinivasUNDERSCOREvelivalaATmentorDOTcom.