May 1, 2019

This two-part article describes advantages when using a hardware emulation platform in virtual mode compared with in-circuit-emulation.

April 26, 2019

Portable Stimulus allows reuse along horizontal, vertical and technique axes, but you need to be aware of the strengths and weaknesses of each to get the greatest benefits.

April 15, 2019

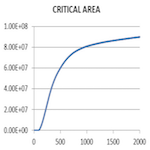

CAA is a valuable tool available to both design engineers and foundries to help them avoid layout-dependent effects during manufacturing.

April 2, 2019

How Chips&Media used HLS on the development of a computer vision IP block.

March 26, 2019

The computational and algorithmic demands made by computer vision systems highlight HLS' value for AI system development.

March 25, 2019

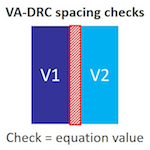

Automated voltage-aware DRC addresses the reliability verification challenges in today’s high-voltage and multiple power domain applications.

March 15, 2019

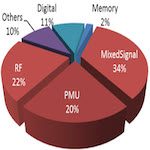

Bob Smith of the ESD Alliance describes how we can promote the ongoing evolution of the design ecosystem.

March 13, 2019

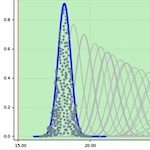

Machine learning techniques help ensure the validity of Liberty Variation Format information for OCV analysis at lower process nodes.

February 27, 2019

This defect and fault injection primer looks at how to standardize definitions, decide injection volume, measure activity, manage simulation, optimize test time and more.

February 8, 2019

How to achieve efficient merging of data from formats such as OASIS, GDS, and OpenAccess to ensure timely verification through DRC runs.