February 29, 2024

How the latest DFT techniques pave the way for quality and success for today's advanced designs.

February 8, 2024

Take a high level view of the AI strategies used within the Tessent family to improve across-the-board performance.

August 27, 2020

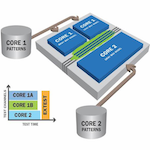

The world of ATPG just changed with the introduction of a new way to create and choose the most effective test patterns.

July 9, 2018

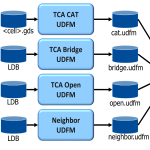

A hierarchical methodology removes DFT from the critical path for large designs. The methodology is compatible with other techniques such as channel sharing, which can further reduce ATPG turn-around time and test cost.

September 21, 2017

Diagnosis-driven yield analysis identifies the cause of systematic yield loss to speed the ramp-to-volume on new processes and improve yield on mature ones.

January 10, 2017

How a new software-led flow speeds silicon bring-up within the Tessent environment, including a Cypress Semiconductor case study.

November 5, 2012

20nm test needs new approaches to cope with short delay defects, new memory failure mechanisms and the consequences of test compression strategies

August 18, 2012

Scan chains help you test complex chip designs. But how do you test the scan chains themselves when they go wrong?

January 24, 2012

The inherent complexity of today’s system-on-chips, with their multiple clock and voltage domains, requires test considerations to be moved further up design flows. The article describes strategies for and benefits from apply test before RTL goes through synthesis, augmenting what is already achieved through memory built-in self test and automatic test pattern generation.