Chiplets to need digital twins for reliability

The added complexity of managing reliability as chiplet-based designs become more common will need to be managed using digital-twin techniques, says a professor working in the field.

Professor Abhijit Dasgupta of the University of Maryland was talking at an online conference on chiplets organized by the MEPTEC trade group this week (July 14, 2021). “Semiconductor and package issues and their failure modes are now merging,” he said. “Reliability engineers belong in every step of development.”

As others as the conference pointed out, Dasgupta said codesign will be an important element of the development process. But reliability will need greater attention and will likely rely on the use of bottom-up physics-based analysis coupled with machine-learning models that try to diagnose problems based on field measurements. The link will be digital-twin databases that could be used to estimate for devices used in infrastructure equipment the remaining useful life of individual parts in the field as well as diagnosing and fixing production issues.

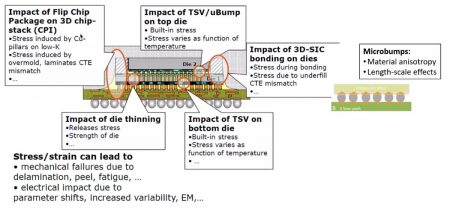

Image Factors affecting chip-package integration reliability

The issues of reliability in chiplet-based products are exacerbated by the likely need to couple devices made on advanced nodes, which are then mixed with those made on older processes that are better understood in terms of reliability. “As we get to smaller nodes, the issues of chip-package interactions are increasing. We have newer materials such as low-k dielectrics that have fragility and poor-adhesion issues,” Dasgupta said.

Other factors include the use of lead-free solders and tiny copper pillars for fine-pitch microbumps. The materials tend towards higher Young’s modulus, which leads to higher stresses in the redistribution layers of substrates. The substrates themselves, which can easily be far larger than a semiconductor reticle, suffer from warpage and large thermal expansion problems. Interactive power management may be needed not just to prevent thermal runaway in dense packages but to avoid the intrapackage connections from failing.

Cooperation will be vital, Dasgupta said. “We are not dealing with new knowledge that we weren’t aware of previously. It is about combining bodies of understanding that exist in different parts of the supply chain.”