February 29, 2024

TCP-Net is Test Case Prioritization using End-to-End Deep Neural Networks and addresses the challenges of today's software-rich projects.

February 8, 2024

Take a high level view of the AI strategies used within the Tessent family to improve across-the-board performance.

September 7, 2022

NVMe over Fabrics (NVMe-oF) extends the memory standard for burgeoning data traffic and the demands of AI and machine learning.

March 2, 2021

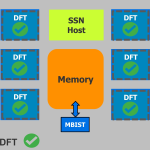

A new technique is especially efficient for AI chips with modular, tiled design strategies leveraging multiple instantiations of the same cores.

February 20, 2020

How can we refine our approach functional verification to deal with the increasing number of systems that leverage artificial intelligence.

September 13, 2019

SEMICON West showed a distinct thematic shift away from preserving Moore's Law to assessing the architectural implications of AI, as EDA was brought into the event.

April 2, 2019

How Chips&Media used HLS on the development of a computer vision IP block.

March 26, 2019

The computational and algorithmic demands made by computer vision systems highlight HLS' value for AI system development.

January 28, 2019

The second part of this feature looks at how Wave Computing's objectives with its dataflow processing unit for AI mapped to the use of emulation in its development.

January 25, 2019

An increasing number of AI players are building their own silicon and finding that emulation is key to overcoming the major challenges.