From iterative to in-design DRC and debug for place and route

One of the biggest headaches place-and-route engineers face is the multiple stop-start iterations of design rule checks (DRCs) that have been made necessary by increasingly challenging power, performance and area (PPA) goals. They slow time-to-market and reduce the time available to optimize and differentiate SoCs.

A new technical paper explains how P&R specialists can now get on-demand in-design DRC verification as they go, using the Calibre RealTime Digital interface, part of the Calibre physical verification family from Siemens EDA.

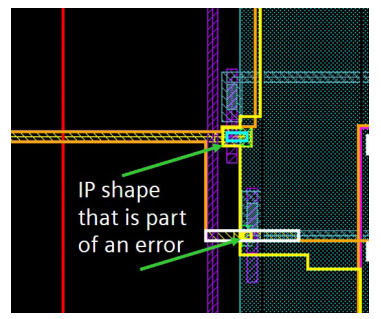

“The traditional signoff DRC closure flow requires exporting design data for the complete hierarchical design, including all the intellectual property (IP) and standard cells in the design, then running signoff DRC. This signoff flow can now be optimized by including manual DRC fixing within the digital design implementation environment using Calibre RealTime Digital,” explains author Swathi Rangarajan.

In ‘Tape out on time with on-demand signoff DRC in P&R’, he takes users through the main challenges, features such as Calibre RealTime Digital’s in-built base layer and metal checks, and how its results viewer helps them cross-probe violations, explore rules and apply appropriate fixes quickly.

An interactive display also allows engineers to try out different fixes to settle on the best option quickly. “DRC error fixing becomes more intuitive, allowing engineers to make optimum DRC fixes in less time, enabling them to qualify the floorplan and proceed forward to the next design phase,” argues Rangarajan.