December 23, 2022

Automating reliability verification with tools that offer packaged checks provides greater consistency and accuracy across an increasingly complex process.

December 23, 2022

Learn how UMVC helps bridge between SystemC and System Verilog using transaction level modeling for test and library efficiency.

October 17, 2022

Fast emerging options, like RISC-V, could foster massive growth in design but verification still needs commercial tools, a Semicon West panel found.

October 6, 2022

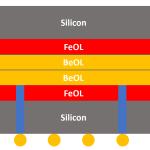

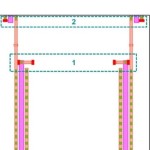

3D-IC presents major connectivity challenges in maintaining a golden netlist and managing necessary exceptions. Learn how to manage them.

September 7, 2022

Symmetry verification for analog and custom IC needs to evolve beyond current time-consuming and hard-to-use techniques.

September 7, 2022

NVMe over Fabrics (NVMe-oF) extends the memory standard for burgeoning data traffic and the demands of AI and machine learning.

May 19, 2022

CDC-related metastability is hard to catch by hand and processes are error prone. Tools offer a more comprehensive approach.

May 10, 2022

Coordinate-based checking provides a streamlined way to verify designs around ESD before full-chip runs without the need for custom checks.

April 28, 2022

What are the options and how do you balance overarching CAD requirements and personal preferences?

March 21, 2022

Automating executable specifications as they evolve can deliver major efficiencies.