Intel talks 4 at VLSI

Intel described the attributes of its upcoming next-generation finFET process at this year’s VLSI Circuits and Technology Symposium.

Using the company’s reworked naming scheme, Intel 4 is the follow-on to the existing Intel 7, formerly 10nm, process: the company claims it delivers a doubling in effective density and a 20 percent performance improvement at the same power.

For the process, Intel has chosen a 50nm gate pitch and 30nm fin pitch along with a 30nm minimum metal pitch, which is similar to the metal pitch chosen by Samsung for its 4nm process. To support power tuning, the process supports four threshold-voltage options for both the NMOS and PMOS transistors, spanning a range of 190mV and 190mV, respectively. With gate scaling factor of around 0.8 over Intel 7, Intel expects the remaining improvement in density to come from the use of a library with a lower track height that takes advantage of a layout that uses fewer dummy gates between cells.

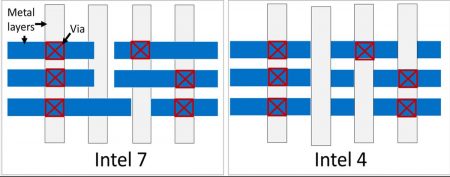

Image A change to gridded layout is intended to improve yield

According to the chipmaker, more extensive use of EUV in place of immersion lithography will simplify the process and improve overall yield. In addition, the company has developed the process to be more compatible with its Foveros and EMIB packaging technologies: supporting a denser microbump pitch on Foveros, with a reduction to 36µm from 50µm. A change to gridded cell layouts is also expected to improve yield as well as performance, due to reductions in capacitance between metal layers that now overlap less.

To help support a smaller metal pitch, Intel has adopted self-aligned pitch quadrupling (SAQP) in the lithography and changed the metal process to use single-damascene patterning together with a more aggressively scaled liner to keep RC parasitics at the same level as Intel 7.