February 6, 2019

UPF provides a useful way to describe the power-management strategies that should be applied to a design, but using it introduces a number of challenges during low-power debugging.

January 28, 2019

The second part of this feature looks at how Wave Computing's objectives with its dataflow processing unit for AI mapped to the use of emulation in its development.

January 25, 2019

An increasing number of AI players are building their own silicon and finding that emulation is key to overcoming the major challenges.

January 25, 2019

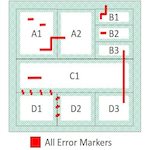

In a continuous-build design flow, at which level should your error markers be addressed?

January 25, 2019

Optimizing the way in which machine learning algorithms are implemented in hardware will be a major differentiator for SoCs, especially for edge devices.

January 16, 2019

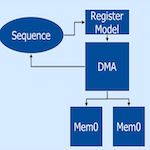

Virtual sequences are considered challenging to write and re-use. Learn how to overcome those issues with the new Portable Stimulus Standard in this DMA-based case study.

January 7, 2019

Escape formal's narrower definitions with a flow that shows you how to Avoid, Detect, Erase, Prove Absence and Tape Out while avoiding bugs.

December 31, 2018

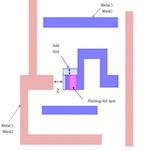

A detailed dive into how MBH strategies for litho hotspots have been enhanced to deal with double patterning at 20nm and below.

December 14, 2018

Antifuse-based OTP NVM is highly scalable, has the area efficiency to enable macros of megabit capacities, and offers low read power.

December 11, 2018

How formal verification for the ISO26262 automotive functional safety delivers the full activation, propagation, and observation in the form of proven and exhaustive results.