September 10, 2019

The Portable Stimulus Standard helps overcome many of the verification challenges inherent in the strict requirements of ISO 26262.

September 9, 2019

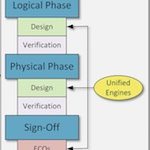

Complex SoCs need systemic optimisation to achieve best time to results, enabled by the use of a unified RTL-to-GDSII flow underpinned by a unified data model.

September 3, 2019

Using a hardware root of trust and a secure development lifecycle process to form the basis of a better approach to developing and implementing more secure complex SoCs.

August 19, 2019

Refactoring saves time and resuources by converting code to a common format and eliminates redundancies to make it more readable and maintainable.

August 15, 2019

Hierarchical DFT for Arm-based SoCs is easier than ever with the arrival of a complete reference flow from Mentor and Arm.

August 9, 2019

Doc Formal rounds up some of the the key observations about verfication made during July’s Synopsys VC Formal SIG event in India.

July 27, 2019

Whether you use OASIS or GDSII, unwanted duplicate cells can make their way into the final SoC database. Learn how to remove them.

July 24, 2019

EV design requires an ability to address interrelated tasks in areas such as architecture, performance, lifetime, range and charging speed.

July 23, 2019

An IDE designed to catch typographical errors, missing declarations and inconsistent references in your code can hugely reduce your time in debug.

July 16, 2019

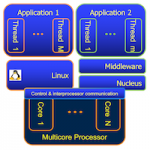

Embedded multicore systems require engineers to make choices around the hardware and software architectures, approaches to certification and more. This is a guide to the trade-offs involved and how to best leverage your options.