October 17, 2022

Fast emerging options, like RISC-V, could foster massive growth in design but verification still needs commercial tools, a Semicon West panel found.

November 4, 2021

PIM memory boosts efficiency by operating on data without moving it to the CPU but realizing this type of novel technology posed power integration and planning challenges.

April 29, 2021

The best paper at DVCon Europe 2020 analyzed different multiclock strategies for SoCs for their power and flexibility

March 2, 2021

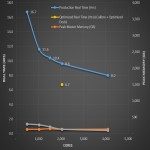

A new technique is especially efficient for AI chips with modular, tiled design strategies leveraging multiple instantiations of the same cores.

July 28, 2020

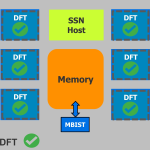

It is easier than ever to build a flexible, resilient, and end-to-end hierarchical DFT flow with smart automation.

May 26, 2020

A Mentor-Microsoft-AMD pathfinder demonstrates the potential benefits of cloud-based physical verification.

April 24, 2020

Learn how the latest design for test innovations deliver efficiency and profitability across the design flow.

November 7, 2019

It's the fiftieth International Test Conference this year. How much has been achieved and how much more work is there to do to ensure that we can keep building chips that do what they are supposed to?

September 9, 2019

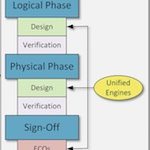

Complex SoCs need systemic optimisation to achieve best time to results, enabled by the use of a unified RTL-to-GDSII flow underpinned by a unified data model.

August 15, 2019

Hierarchical DFT for Arm-based SoCs is easier than ever with the arrival of a complete reference flow from Mentor and Arm.