April 1, 2013

You can waive some physical verification errors related to legacy IP found in foundry DRC checks. Knowing which has involved lengthy manual analysis. TSMC is enhancing the process with automation.

March 11, 2013

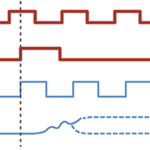

The multiple clock domains on today's SoCs create a hotbed for clock-domain crossing bugs to thrive. Low-power design techniques increase the complexity of tracking these bugs down. Find out how these failures arise and what to do about them.

February 5, 2013

Cache coherency implemented in hardware increases the verification effort. VIP-based strategies are described with particular reference to ARM protocols.

January 31, 2013

Trying to balance your use of simulation and FPGA prototyping is tough. Acceleration used with Accelerated VIP offers simulation-like visibility and debug with near FPGA performance.

January 24, 2013

How should you quiz your verification IP vendor to get the right VIP for your needs? Synopsys' Neill Mullinger details a checklist of the key points to raise.

January 18, 2013

This case study shows how the evaluation of various design options requires a thorough approach to system-level modeling.

December 12, 2012

Meeting the challenges of moving beyond planar integration to side by side, and eventually truly stacked, dice, for designers, tool vendors and the supply chain.

December 6, 2012

Using hierarchy and improved constraints management to accelerate static timing analysis at 20nm and below.

December 4, 2012

finFETs are vital to the next generation of CMOS processes from Intel, TSMC and others. How will process issues including bulk vs SOI substrates, density limitations, thickness control, and planar device integration affect their practical implementation?

December 3, 2012

CSR used a customized approach to automated dummy fill layout for AMS to address layer density and device matching issues in standard flows aimed at digital SoCs.