May 8, 2013

Many design teams are looking at ways in which they can make use of 3D integration. Here are eight requirements for an effective 3D-IC design flow.

May 7, 2013

Better upfront analysis can help avoid propagating errors from RTL into the netlist, and reveal a number of ways to improve the quality of your final design.

May 2, 2013

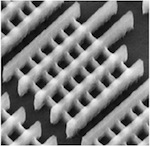

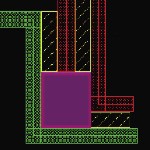

A look at some of the design and physical verification challenges of working with finFET and FD-SOI devices, including their impact on layout, DRC and LVS.

April 24, 2013

Many problems arise during the IP-to-SoC phase of FPGA-based prototyping due to the mix-and-match nature of the prototypes not the actual designs.

April 22, 2013

The arrival of the 20nm and finFET-based 14nm and 16nm processes bring with them challenges for custom IC design. These are the five key areas and a methodology that can address them.

April 17, 2013

2.5D-IC integration overcomes 2D limitations such as cost, offchip bandwidth bottlenecks and I/O pin scarcity, and offers a route to true 3D-IC integration.

April 10, 2013

It’s time to take up the challenge of applying 3D integration technology to IC design. The manufacturing process technology is maturing, the tool chains are in place, and the opportunities to broaden your market by applying a new form of systemic integration are growing.

April 10, 2013

An increasingly important concept in design is that of product creation. An approach based on product creation looks beyond chip or board design.

April 9, 2013

The chipmaker used Calypto’s PowerPro to carry out power analysis of its latest core design at the RTL rather than at post-gate synthesis.

April 4, 2013

Debug of logic and testbench debug makes up 35% of chip design, and is growing as power-management and hardware/software issues become part of the task.