March 1, 2016

The reset state of a design can have a huge impact on the scope and correctness of verification, especially when formal techniques are applied.

April 16, 2014

Reset is no longer simply an 'X' issue but also feeds into power optimization. Catching issues early greatly speeds verification.

January 27, 2014

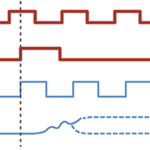

Find how to spot some of the most common false clock-domain crossing (CDC) violations and how to efficiently find actual CDC problems that could kill a design if not corrected.

October 31, 2013

X propagation within RTL simulations can hide fatal bugs. Uncovering and eliminating the effect improves design quality and avoids respins.

March 11, 2013

The multiple clock domains on today's SoCs create a hotbed for clock-domain crossing bugs to thrive. Low-power design techniques increase the complexity of tracking these bugs down. Find out how these failures arise and what to do about them.