September 28, 2020

And when this key architectural decision might involve combining both depending on your design’s use-case and demands placed upon it.

September 25, 2020

VHDL has come a long way in terms of complexity. An integrated development environment helps you deliver better and more compliant code quickly.

September 24, 2020

Model-based systems engineering is a necessary next-step in methodology to cope with the broadening range of innovation across automotive, aerospace and other vehicular markets.

September 21, 2020

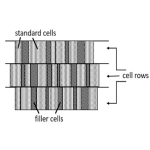

A physical verification-ready flow can speed project delivery by making your use of filler cells more efficient.

September 7, 2020

But you were NOT afraid to ask.... It's time for some answers.

August 27, 2020

The world of ATPG just changed with the introduction of a new way to create and choose the most effective test patterns.

August 25, 2020

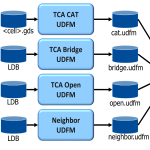

How Calibre is evolving to address the challenges of LVS verification in early-stage design.

August 14, 2020

For physical verification and beyond, each process node requires new thinking, new tools and greater performance.

August 12, 2020

Learn how an IDE offers on-the-fly, auto-correct and informed analysis of VHDL code to speed project quality and delivery.

July 28, 2020

It is easier than ever to build a flexible, resilient, and end-to-end hierarchical DFT flow with smart automation.