March 13, 2019

Machine learning techniques help ensure the validity of Liberty Variation Format information for OCV analysis at lower process nodes.

March 6, 2019

The doctor was 'in' during last month's DVCon and here highlights some of the main issues in formal raised by delegates at the verification conference.

March 1, 2019

Application-specific processors can provide high performance for specialised tasks at low energy cost.

February 8, 2019

How to achieve efficient merging of data from formats such as OASIS, GDS, and OpenAccess to ensure timely verification through DRC runs.

February 6, 2019

UPF provides a useful way to describe the power-management strategies that should be applied to a design, but using it introduces a number of challenges during low-power debugging.

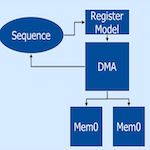

January 16, 2019

Virtual sequences are considered challenging to write and re-use. Learn how to overcome those issues with the new Portable Stimulus Standard in this DMA-based case study.

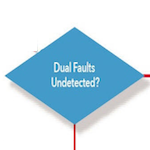

January 7, 2019

Escape formal's narrower definitions with a flow that shows you how to Avoid, Detect, Erase, Prove Absence and Tape Out while avoiding bugs.

December 11, 2018

How formal verification for the ISO26262 automotive functional safety delivers the full activation, propagation, and observation in the form of proven and exhaustive results.

December 3, 2018

The verification challenges of using low-power design techniques to enable advanced power-management strategies in complex SoCs.

November 20, 2018

Adoption of high-density advanced packaging (HDAP) needs tools and supports to build designers' confidence in the emerging technology.