Vivado, inside the new Xilinx design suite

The FPGA vendor’s new flagship is now on public release. It adds an array of features, including support for system-level to HDL synthesis.

The Vivado Design Suite has been released by Xilinx after four years of development and a year of beta testing. It is a highly integrated design environment with a completely new generation of system-to-IC-level tools, all built on the backbone of a shared scalable data model and a common debug environment.

The suite significantly boosts runtime, and incorporates support for industry standards such as C+/C++/SystemC, the AMBA AXI4 interconnect, IP-XACT IP packaging metadata, the Tool Command Language (Tcl), SystemVerilog and Synopsys Design Constraints (SDC).

Xilinx architected Vivado to enable the combination of all types of programmable technologies and to scale up to 100 million ASIC equivalent-gate designs.

‘All programmable’

Vivado reflects Xilinx’ concept of ‘All programmable devices‘. These enable customers to achieve higher levels of programmable systems integration, increase system performance, lower BOM cost and total system power consumption, and accelerate design productivity

The concept goes beyond the traditional FPGA heartland of programmable logic and I/O into areas such as software-programmable ARM subsystems, 3D ICs and analog mixed signal. To achieve this, Vivado directly addresses nagging integration and implementation design-productivity bottlenecks.

Examples of the integration bottlenecks include

- integrating algorithmic C and register-transfer level (RTL) IP;

- mixing the DSP, embedded, connectivity and logic domains;

- verifying blocks and ‘systems’; and

- reusing designs and IP.

Examples of implementation bottlenecks include:

- hierarchical chip planning and partitioning;

- multi-domain and multi-die physical optimization;

- multi-variant ‘design’ vs. ‘timing’ closure; and

- late-stage engineering change orders (ECOs) and the rippling effects of design changes.

More specific detail on how Vivado addresses these issues follows, but as a taster, new features include comprehensive cross-probing of many reports and design views, state-of-the-art graphics-based IP integration and the first fully supported commercial deployment of high-level synthesis (C++ to HDL) by an FPGA vendor (read more on the Vivado HLS/AutoESL technology underpinning this in this sister article’s case study with Agilent).

Xilinx introduced its hitherto flagship ISE Design Suite in 1997. Ut featured a then innovative timing-driven place-and-route engine. Over the subsequent decade and a half, the company added technologies such as multi-language synthesis and simulation, IP integration and a host of editing and test utilities. ISE grew to match FPGAs’ own increasing capability to address ever more complex functions.

For Vivado, Xilinx has drawn upon lessons learned from ISE. It has taken across key technologies while also leveraging modern EDA algorithms, tools and techniques. Vivado has been designed with the incoming 20nm node in mind, and so that it can also scale into the foreseeable future.

Meanwhile, Xilinx will develop and support ISE indefinitely for customers targeting 7 series and older technologies. Going forward, however, Vivado now becomes the flagship design environment, supporting 7 series and future devices.

Deterministic design closure with Vivado

At the heart of any FPGA vendor’s design suite is the physical-implementation flow: synthesis, floorplanning, placement, routing, power and timing analysis, optimization and ECO.

To reduce iterations and design time and improve productivity, Xilinx has built Vivado’s implementation flow using a single, shared, scalable data model. This framework is already found in advanced ASIC design environments.

The model allows all steps in the flow to operate on an in-memory data model that enables debug and analysis at every step. This gives much earlier visibility into key metrics such as timing, power, resource utilization and routing congestion. These estimates become progressively more accurate as the design progresses.

The unified data model allows for tight links between a multidimensional, analytical place-and-route engine and both the suite’s RTL synthesis engine and new multiple-language simulation engines. The same links extend as well to individual suite tools such as Vivado’s IP Integrator, Pin Editor, Floor Planner and Device Editor.

Customers can use a comprehensive cross-probing function to follow a given problem from schematics, timing reports or logic cells to any other view and all the way back to HDL code. This provides analysis at and connects every step of the design process.

Vivado also provides analysis for timing, power, noise and resource utilization at every stage after synthesis. So, if the user learns early on that timing or power is far off specification, he can make short iterations to address the issue proactively rather than run long iterations after place-and-route.

The tight integration afforded by the scalable data model enhances the effectiveness of pushbutton flows for users who want maximum automation, where their tools do the vast majority of the work. At the same time, it gives users who require more advanced controls better analysis and command of every design move.

Hierarchical chip planning, fast synthesis

Vivado lets users partition a design for processing by synthesis, implementation and verification. It promotes a divide-and-conquer team approach to big projects. A new design-preservation feature provides repeatable timing results and the ability to perform partial reconfiguration.

The suite also includes an entirely new synthesis engine that is designed to handle millions of logic cells. Key to this is enhanced support for SystemVerilog.

The synthesis engine’s use of the synthesizable subset of SystemVerilog makes it three times faster than XST, the Xilinx Synthesis Technology in the ISE suite, and includes a ‘quick’ option that lets designers rapidly get a feeling for area and size. They can then debug 15 times faster than before with an RTL or gate-level schematic.

With more ASIC designers moving to programmable platforms, Vivado also leverages Synopsys Design Constraints throughout the flow. The use of this and other standards opens up new levels of automation where customers can now access the latest EDA tools for tasks such as constraint generation, cross-domain clock checking, formal verification and static timing analysis.

Vivado’s multidimensional analytical placer

Older FPGA vendor design suites use one-dimensional timing-driven place-and-route engines powered by simulated annealing algorithms that determine randomly where the tool should place logic cells.

With these routers, users enter timing, then the simulated annealing algorithm pseudorandomly places features, seeking a ‘best as it can’ match for timing requirements. This made sense when designs were much smaller and logic cells were the main cause of delays. Today, interconnect and design congestion contribute far more.

Place-and-route engines with simulated annealing algorithms do an adequate job for FPGAs below one million gates. But they underperform as designs grow beyond that. They struggle with congestion and the results become increasingly unpredictable.

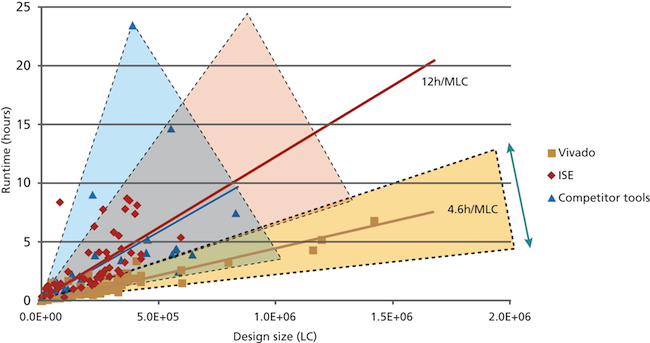

Xilinx has developed a multidimensional analytic placement engine for Vivado on a par with those found in million-dollar ASIC place-and-route tools. It analytically finds a solution that primarily minimizes three dimensions of a design: timing, congestion and wire length. The engine does this while taking the entire design into account instead of taking the local-move approach of simulated annealing. As a result, the tool can place and route 10 million gates quickly, deterministically and with consistently strong results (see Figure 1). Also, because it is solving for three factors simultaneously, it requires fewer iterations.

Figure 1

Vivado’s placement engine claims to match expensive P&R tools (Source: Xilinx – click image to enlarge)

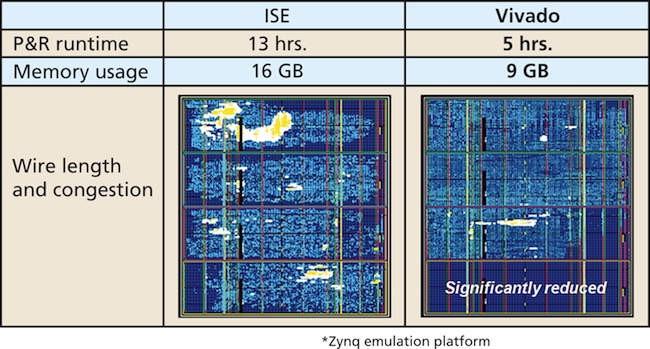

Xilinx ran the raw RTL for its Zynq-7000 EPP emulation platform, a very large and complex design, in the pushbutton modes of both ISE and Vivado. Each tool was instructed to target Xilinx’s largest FPGA device, the SSI-enabled Virtex-7 2000T FPGA.

Figure 2

Vivado benchmarked on the Zynq emulation platform (Source: Xilinx – click image to enlarge)

Vivado’s place-and-route engine took five hours to place the 1.2 million logic cells; ISE v13.4 took 13 hours (Figure 2). The Vivado Design Suite also implemented the design with less congestion (as seen in the gray and yellow portions) and in a smaller area, reflecting the total wire-length reduction.

Further, the Vivado implementation had better memory compilation efficiency, taking only 9Gbyte to implement the design’s required memory to ISE’s 16Gbyte. Finally, Vivado only utilized three-quarters of the device to implement its version of the design.

Power optimization and analysis

Vivado incorporates up-to-date power-optimization strategies such as advanced clock-gating which it uses to, for example, can analyze design logic and remove unnecessary switching activity. Specifically, it focuses on the switching-activity factor ‘alpha’. The technique can achieve up to a 30 per cent reduction in dynamic power.

Also, the new shared scalable data model means that users can get power estimates at every stage, enabling up-front analysis so that problem areas can be addressed early on.

Simplifying ECOs with Vivado

Incremental flows allow users to quickly process minor design changes by reimplementing a small part of the design, making iterations faster. They also enable performance preservation after each incremental change, thus reducing the number of iterations overall.

Vivado includes an extension to the popular ISE FPGA Editor tool, the Vivado Device Editor. Using the editor on a placed-and-routed design gives designers the power to make late-stage ECOs (e.g., move instances, reroute nets, tap a register to a primary output for debug with a scope, change the parameters on a digital clock manager or a lookup table) without going back through synthesis and implementation.

Automation, not dictation

The Vivado tool team adopted a philosophy of automating, not dictating the way people design. However the user starts (C, C++, SystemC, VHDL, Verilog, SystemVerilog, MATLAB or Simulink) and whoever’s IP they use (Xilinx or third-party), Vivado offers a way to automate those flows and boost productivity.

The top priority was to give the suite specialized IP features that facilitate the creation, integration and archiving of intellectual property. There are new IP capabilities in Vivado: IP Packager, IP Integrator and the Extensible IP Catalog. More than 20 vendors already offer IP supporting the suite and these features.

IP Packager allows Xilinx customers, IP developers and ecosystem partners to turn any part of a design — or indeed, the entire design — into a reusable core at any level of the design flow: RTL, netlist, placed netlist and placed-and-routed netlist. The tool creates an IP-XACT description of the IP for easier integration into future designs. The IP Packager specifies the data for each piece of IP in an XML file. Once the IP is packaged, IP Integrator can stitch it into the rest of a design.

IP Integrator allows customers to integrate IP into their designs at the interconnect level rather than at the pin level. The user can drag and drop pieces of IP onto a design and the tool will check upfront that the respective interfaces are compatible. If they are, the user draws one line between the cores and the integrator automatically writes detailed RTL to connects the pins.

The output of that process can then be run back through the IP Packager. The result becomes a piece of IP that other people can reuse and is, as noted above, available in multiple formats.

The Extensible IP Catalog allows users to build their own standard repositories from IP they have created or licensed from Xilinx and third-parties. The catalog conforms to the IP-XACT standard, and this allows design teams and even enterprises to better organize their IP and share it across an organization.

Both the Xilinx System Generator and IP Integrator are part of the Vivado Extensible IP Catalog so that users can easily access catalogued IP and integrate it. Instead of third-party vendors delivering IP in a zip file and with various deliverables, they can now deliver it to you in a unified format that is instantly accessible and compatible with the Vivado suite.

Mainstream high-level synthesis for FPGAs

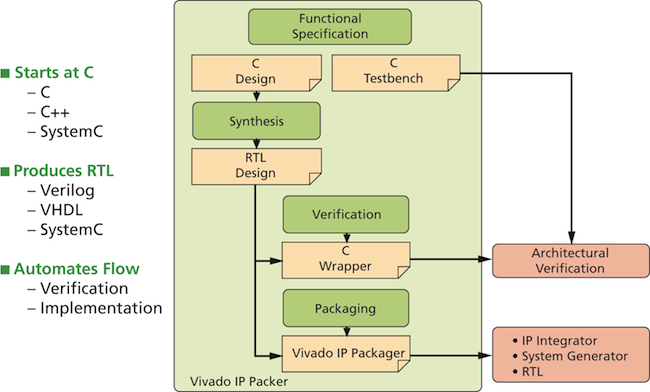

Perhaps the most forward looking technology in the new suite is Vivado HLS (high-level synthesis), which Xilinx gained through its acquisition of AutoESL in 2010.

Vivado HLS provides comprehensive coverage of C, C++ and SystemC, and carries out floating-point as well as arbitrary precision floating-point calculations. This means that you can work with the tool in an algorithm-development environment rather than a typical hardware environment.

A key advantage of doing this is that algorithms developed at that level can be verified orders of magnitude faster than at the RTL. That provides not only simulation acceleration but also the ability to explore the feasibility of algorithms and then make, at then architectural level, trade-offs in terms of throughput, latency and power.

Designers can use Vivado HLS in many ways to perform a wide range of functions. Consider this demonstration in the form of a common flow for developing IP and integrating it into designs.

- Create a C, C++ or SystemC representation of the design and a C testbench that describes its desired behavior.

- Verify the system behavior of the design using a GNU Compiler Collection/G++ or Visual C++ simulator.

- Get the behavioral design functioning satisfactorily and settle the accompanying testbench.

- Run the design through Vivado HLS synthesis to generate RTL (Verilog or VHDL).

- Use the RTL to perform Verilog or VHDL simulation of the design or have the tool create a SystemC version using the C-wrapper technology.

- Perform a SystemC architectural-level simulation and further verify the architectural behavior and functionality of the design against the previously created C testbench.

- (a) Once the design has been solidified, put it through the Vivado Design Suite’s physical-implementation flow to program it into a device and run it in hardware; or (b). Using the IP Packager to turn the design into a reusable piece of IP, stitch the IP into a design using IP Integrator or run it in System Generator.

Figure 3 offers another perspective on a Vivado flow.

Figure 3

Flexible options within Vivado (Source: Xilinx – click image to enlarge)

This is merely one way to use the tool. You can see how Agilent’s Nathan Jachimiec and Xilinx’s Fernando Martinez Vallina used the Vivado HLS technology (called AutoESL technology in the ISE Design Suite flow) to develop a UDP packet engine for Agilent in this article.

Xilinx has also created Vivado Simulator, a new mixed-language simulator for the suite that supports Verilog and VHDL. With a single click of a mouse, users can launch behavioral simulations and view results in an integrated waveform viewer. Simulations are accelerated at the behavioral level using a new performance-optimized simulation kernel that executes up to three times faster than the ISE simulator. Gate-level simulations can also run up to 100 times faster using hardware co-simulation.

Vivado availability

Where Xilinx offered the ISE Design Suite in four editions aimed at different types of designers (Logic, Embedded, DSP and System), the company will offer the Vivado Design Suite in two editions.

The base Design Edition includes the new IP tools in addition to Vivado’s synthesis-to-bitstream flow.

Meanwhile, the System Edition includes all the tools of the Design Edition plus System Generator and Xilinx’s new Vivado HLS.

The Vivado Design Suite version 2012.3 is available now and will be followed by WebPACK availability later this year. ISE Design Suite Edition customers with current support receive the new Vivado Design Suite Editions in addition to ISE at no additional cost.

For more information on downloading Vivado, click here.

A series of video tutorials is also available.

This article originally appeared in Issue 79 of Xcell Journal. Many thanks to them and Xilinx for permission to reproduce this version. To read the extended original, download the issue here. For more on the magazine, click here.

Contact

Xilinx, Inc.

2100 Logic Drive

San Jose

CA 95124-3400

USA

T: +1 408 559 7778

W: www.xilinx.com