SystemC

What is SystemC?

SystemC is an extension of the C++ programming language that can be used to create an executable model of a system that is made up of an as-yet undefined combination of hardware, software and data flows between them.

SystemC is implemented as a class library that adds hardware modelling constructs, such as concurrency, clocks, modules and interconnections, to the core C++ language.

As the IEEE Language Reference Manual for the library puts it “The SystemC class library supports the functional modeling of systems by providing classes to represent the following:

- The hierarchical decomposition of a system into modules

- The structural connectivity between those modules using ports and exports

- The scheduling and synchronization of concurrent processes using events and sensitivity

- The passing of simulated time

- The separation of computation (processes) from communication (channels)

- The independent refinement of computation and communication using interfaces

- Hardware-oriented data types for modeling digital logic and fixed-point arithmetic”

The SystemC class library includes an event-driven simulation kernel. When the source files for the system design and its test benches are compiled and linked with the SystemC class library, the result is an executable system simulation that can be used to check that the correct function has been implemented, and which can then act as a golden reference model for the rest of the design process.

What does it do and why?

SystemC can help increase productivity by offering a more abstract way of defining a system than is available using hardware description languages (HDLs) such as Verilog and VHDL.

The abstract nature of SystemC enables systems to be specified independent of their implementation. This gives designers the freedom to explore various architectural approaches and to make trade-offs between software and hardware before committing to an implementation path for each functional block.

SystemC also offers a rich set of datatypes, which can be used to define functions at various abstraction levels, from highly abstract down to the cycle-accurate register-transfer level.

SystemC is also claimed to offer a smoother path to hardware than approaches that model a system in C or C++ and then have to translate that model into an HDL and verify the accuracy of that conversion before starting on the path to implementation.

The basic buildings blocks of SystemC include:

- Modules, which are used to partition a design. Modules communicate with each other through interfaces, and hide their internal data representation from other modules. Modules can include ports, exports, channels, processes, events, instances of other modules, other data members, and other member functions.

- Processes, which model the functionality of the system.

- Ports, which provide the routes through which information is passed to and from a module.

- Channels, which provide the ‘wiring’, or communication elements, of SystemC, and which can be defined as anything from a simple wire to a more complex mechanism such as a FIFO.

- Interfaces, which ports use to communicate with channels.

- Clocks, a special object that defines a clock signal in terms of its period, duty ratio, offset and initial value.

- Events, which enable synchronization between processes.

- Data types, including several defined in SystemC, as well as support for user-defined types.

The latest version of the SystemC specification supports transaction-level modelling (Guide), another technique for raising the level of abstraction in system definition and creating consistent frameworks that can be used to integrate system components expressed at many different levels of abstraction. The greater level of abstraction can also accelerate simulation, especially in complex multicore designs.

To find out more about the latest version of the SystemC library, published in early 2012, check out the blog from Dennis Brophy, vice chair of the Accellera Systems Initiative.

Where can I use SystemC?

SystemC can be used to create an executable specification for a system before any hardware has been defined or software written. This makes SystemC useful for:

- architectural exploration

- virtual prototyping

- performance modelling

- software development

- functional verification

- a starting point for high-level synthesis.

A finalised SystemC description can act as a golden reference model with which later elaborations of the design can be compared.

Can I buy it?

No need. The latest version of the SystemC language (SystemC 2.2.0) is available here. The IEEE ratified a version of SystemC as IEEE1666-2011 in November 2011.

Who is involved with SystemC?

The development of SystemC has been underway for more than a decade and has drawn on technology and talent from across the electronics design community.

Accellera, which was founded with the merger of VHDL International and Open Verilog International in 2000, did extensive work developing enabling standards such as System Verilog, the Unified Verification Methodology, and VHDL among others. At the same time, the Open System C Initiative, founded in 1999, worked on developing SystemC. The two groups merged in 2011 to form the Accellera Systems Initiative as an “independent, not-for profit organization dedicated to creating, supporting, promote, and advancing system-level design, modelling, and verification standards”, with a very broad membership.

Some of the Accellera Systems Initiative members also sit on the IEEE working group, P1666, which helps formalise SystemC as an IEEE standard. Voting members of the working group include Accellera, Cadence Design Systems, Freescale, Intel, JEITA, Mentor Graphics, NXP, OSCI, STMicroelectronics, STARC, Synopsys and TI.

What are the risks of using SystemC?

SystemC has been in development for over a decade, and has been through two rounds of ratification as an IEEE standard, in 2005 and 2011. It is backed by a broad vendor base and draws on technical insights from a broad community of developers and users.

What risks are involved in using SystemC? Here are some issues to consider:

- SystemC is still an evolving language, so designs written in SystemC today may not carry forward (this is true for many programming languages)

- Like other system modelling languages, SystemC is likely to become a focus for a ‘clash of cultures’, between engineers coming from hardware and software backgrounds. Hardware engineers may not be comfortable with the object-oriented basis of the underlying C++ language; software engineers may not understand the hardware implications of the code they write.

- Routes from SystemC to hardware implementation, such as high-level synthesis, are still evolving, so the process of decomposing a design from SystemC to gates and assembler may not be as smooth as suggested.

- SystemC is an extension of C++, which was developed for other purposes. This leaves the door open for the emergence of a more highly optimised system modelling language in future.

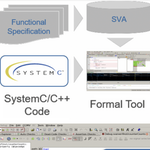

Formal verification for SystemC/C++ designs

Take advantage of the automated refactoring of design and verification code

Correct design and verification coding errors as you type

DVCon China launches this April in Shanghai

Linking high-level synthesis with formal verification