October 11, 2013

Verify registers without writing code for specific bus interfaces or speed up the loading of configuration registers using the UVM Register Layer. Videos show you how.

July 31, 2013

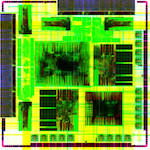

How the company migrated to an OVM-based methodology to design and verify a 30 million-gate ASIC design, on the path to UVM.

May 23, 2012

VHDL is a hardware description language with rich constructs that can model complex systems. It can also be constrained for use as the starting point of an FPGA or ASIC design.

April 5, 2012

More than half of design companies claim to use ABV but many have yet to deploy full methodologies.

March 28, 2012

Verification IP is becoming an increasingly important component for system design due to the rapid proliferation of new protocols and interfaces, chiefly driven by mobile comms.

August 23, 2011

Bridging the analog-digital divide is tough, particularly when it comes to verification. The two domains are marked by a host of differences with regard to tools, methodologies and the basic means of developing and testing designs. Analog engineers do most of their work by building and moving graphics while their digital counterparts do most of [...]

August 23, 2011

Mentor’s Dennis Brophy, Cadence’s Stan Krolikoski and Synopsys’ Yatin Trivedi describe how you can prepare to adopt Accellera’s Universal Verification Methodology.

February 25, 2011

Your current verification strategy, no matter how robust, may not always satisfy the latest demands placed upon it given the rate of change in semiconductor design. To stay at the forefront of innovation, you must be willing and able to take advantage of the potential in emerging and evolving technologies. It is not simply that […]

February 25, 2011

The article describes a methodology and appropriate code for developing a reset strategy that will work within a verification process. Specifically, the proposal has been drafted within the terms of the Open Verification Methodology.

February 25, 2011

Constrained random testbenches excel at quickly hitting the majority of coverage but their effectiveness trails off as coverage closure nears completion. This paper describes a testbench API that sits on top of OVM sequences allowing the existing constrained random infrastructure to be guided, enabling faster, more efficient coverage closure. Design and verification engineers can use [...]