January 12, 2022

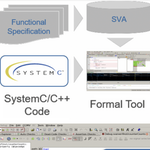

Automated formal technologies can be used to ease the debug and functional verification burden of SystemC/C++ code prior to high-level synthesis. This tutorial, first presented at DVCon Europe explores how these formal techniques can be deployed and provides real-world examples.

August 31, 2017

Doc Formal concludes his introduction to formal verification with a practitioner's view of the technology.

January 5, 2016

Using formal property verification to prove that SoCs can’t do the wrong thing, as well as that they will do the right thing.

June 30, 2015

Considering design style, assertions, engines and coverage can help ease the development of an effective formal verification test plan

May 29, 2015

Research study suggests the maturity of your verification flow determines the likelihood of first-pass success far more than the complexity inherent in design size.

January 20, 2015

Combining assertion-based verification techniques with emulation makes for easier debug, better coverage and greater functional efficiency.

May 29, 2014

A static-analysis tool that checks for errors in HDL code, lint is becoming an increasingly important addition to simulation for RTL and SoC signoff.

May 28, 2014

As designs get larger and stress the ability of simulation to exercise an SoC, formal techniques have become essential parts of design and verification.

May 19, 2014

Verification coverage attempts to at least provide a partial answer to the question: "How do you know you are finished verifying?" It involves the combination of a number of techniques.

April 5, 2012

More than half of design companies claim to use ABV but many have yet to deploy full methodologies.