June 9, 2020

A collaboration between GlobalFoundries and Mentor has resulted in an innovative in-design fixing strategy across markets such as IoT, mobile, RF, graphics and networking.

April 14, 2020

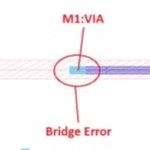

Early detection using design integrity checks during implementation from abstract LEF/DEF inputs can deliver major efficiencies.

February 14, 2020

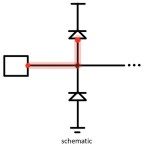

P2P (point-to-point) resistance is fundamental to IC reliability verification. Handle it more efficiently with detailed, automated path layout analysis.

October 9, 2019

Learn how XML-based constraints can standardize rule development and use with coding examples for the Calibre PERC reliability platform.

July 27, 2019

Whether you use OASIS or GDSII, unwanted duplicate cells can make their way into the final SoC database. Learn how to remove them.

June 11, 2019

How to remove or extract portions of a layout for easier, more focused and faster project delivery.

March 25, 2019

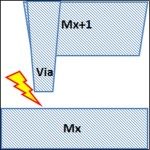

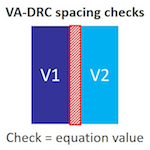

Automated voltage-aware DRC addresses the reliability verification challenges in today’s high-voltage and multiple power domain applications.

May 15, 2017

This second part looks at Mentor's views on flow neutrality, how DRS360 was born, machine learning and the threat from embedded Trojans.

December 9, 2013

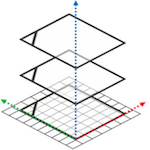

Extracting finFET parasitics means a shift to 3D models, field solvers for greater accuracy, and MCMM techniques.