October 11, 2013

PGA has been IC-centric for mainstream 2D configurations. It must become system-centric for 2.5D and 3D systems.

September 24, 2013

Mobile and networking platforms need high bandwidth, low power consumption, and small footprint. These needs drove standards, such as LPDDR4, Wide I/O 2 and Hybrid Memory Cube.

August 12, 2013

3D-IC design is ready for take-off, following several years of intense collaboration to develop the necessary tools, methodologies and flows

May 8, 2013

Many design teams are looking at ways in which they can make use of 3D integration. Here are eight requirements for an effective 3D-IC design flow.

April 17, 2013

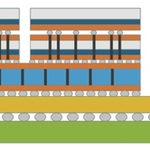

2.5D-IC integration overcomes 2D limitations such as cost, offchip bandwidth bottlenecks and I/O pin scarcity, and offers a route to true 3D-IC integration.

April 10, 2013

It’s time to take up the challenge of applying 3D integration technology to IC design. The manufacturing process technology is maturing, the tool chains are in place, and the opportunities to broaden your market by applying a new form of systemic integration are growing.

December 12, 2012

Meeting the challenges of moving beyond planar integration to side by side, and eventually truly stacked, dice, for designers, tool vendors and the supply chain.

November 16, 2012

The advantages and challenges of 3D IC integration, as we add vertical functional integration options to the traditional planar integration brought by the progress of Moore's Law.

August 21, 2012

A guide to emerging 3D integration techniques for ICs, including a look at various approaches, and some of the tools and standards issues involved.

December 14, 2010

Sematech, the leading research consortium for semiconductor manufacturing, has launched a campaign to recruit members from the fabless sector. The move reflects the importance of making manufacturing decisions earlier in the design flow, and is also intended to get input from designers on implementations of such technologies as 3D interconnects, next-generation lithography and novel materials/structures.