February 4, 2014

The fourth installment discusses the extra levels of debug capability available when using virtual prototypes through the example of an ARM big.LITTLE-based embedded system.

December 16, 2013

Continuing our series on high-level synthesis (HLS) for low power design. Part Two details how HLS helps you make and evaluate architectural decisions.

October 21, 2013

Going inside HLS' basics shows how it can deliver power savings over 50% for some applications.

October 7, 2013

Build tools around the dataflows and control systems engineers model to address verification challenges posed by burgeoning complexity and low power.

June 2, 2013

IEEE 1801-2013 updates and refines the Unified Power Format for low-power VLSI design, reflecting changes in power modeling and verification.

April 9, 2013

The chipmaker used Calypto’s PowerPro to carry out power analysis of its latest core design at the RTL rather than at post-gate synthesis.

March 11, 2013

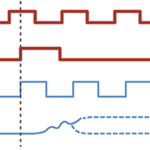

The multiple clock domains on today's SoCs create a hotbed for clock-domain crossing bugs to thrive. Low-power design techniques increase the complexity of tracking these bugs down. Find out how these failures arise and what to do about them.

October 30, 2012

An exclusive extract from Cadence Design Systems' Mixed-Signal Methodology Guide provides an excellent overview of its discrete topic and a flavor of the book as a whole.

October 26, 2012

Overcome the time and visibility limitations of simulation and of gate-level and RTL-based strategies to achieve full-chip analysis.

October 15, 2012

OpenCL aims to open up the performance of graphics processors to other applications. It is also one more way in which compilation is being moved to runtime to make it easier to move code dynamically across heterogeneous platforms.