Overcome reset domain crossing challenges when using UPF

NXP Semiconductors and Siemens EDA have publicly released a technical paper that describes issues that require refinement in the use of the Unified Power Format (UPF) due to the potential introduction of metastability into the reset domain crossing space because of UPF instrumentation. The work was originally presented at DVCon 2021.

The research is based on experiences with a real-world SoC design. “We… show how low power UPF strategies, like the insertion of isolation cells, can have a huge impact on the reset strategy, as the number of new resets increase dramatically,” write authors Inayat Ali of NXP and Abdul Moyeen, Manish Bhati, Manjunatha Srinivas of Siemens.

“These issues if undetected, may result in a higher verification turnaround time and unnecessary ECOs, resulting in costly respins.”

The paper proposes RDC-led refinements to a UPF methodology and checks that can be added where they are not available in current static verification tools.

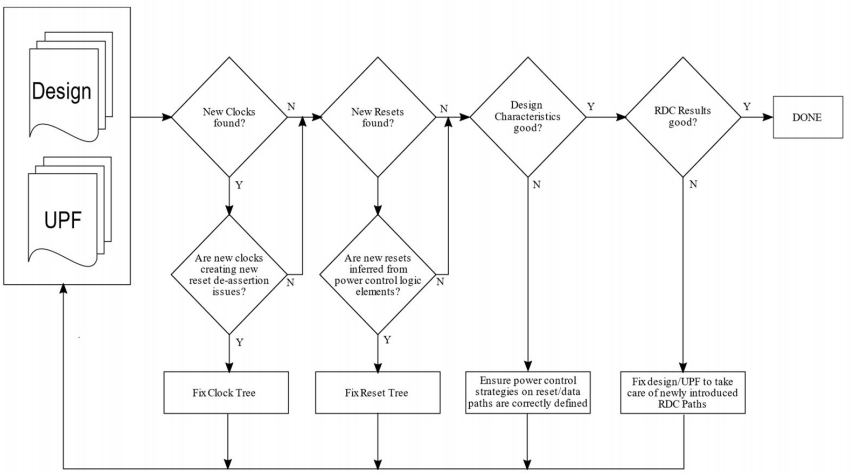

The main problematic RDC scenarios concern, the authors say, isolation logic, level shifter logic, retention cell logic. Eleven scenarios are specifically identified, alongside the extra checks and the methodology (also shown in Figure 1).

Figure 1. Methodology for power-aware RDC (NXP Semiconductors/Siemens EDA/Accellera – click to enlarge)

The refined UPF methodology has five new components:

- Adding power control logic may lead to higher number of resets. All the new resets must be resolved before doing RDC analysis.

- Adding power control logic may lead to higher number of clocks leading to higher reset domain crossings spanning different clock domains as well as reset de-assertion issues. All the new such clocks must be resolved before doing RDC analysis.

- Adding power control logic may disrupt existing Reset ordering. Review the newly created resets by examining the reset tree report and check if the newly created reset has in its fan-in a reset which is a part of an existing reset order.

- If possible, ensure that the control signals of the power control logic are from the Rx reset power domain.

- Incorrect clamp values of power control strategies can reset the fan-out logic incorrectly. Ensure correct clamp values are defined in the UPF.

Bringing Reset and Power Domains Together is available for download here.