low power

Sleep modes

How TI halved the power consumption of Wolverine

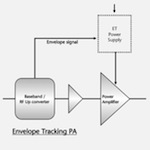

Envelope tracking for RF power amplifiers in mobile handsets

Unified Power Format (UPF)

Energy debugging – the next step in MCU software optimization

Winning the power and temperature battle with ESL exploration

Part 4- Power management in OCP-IP 3.0

According to Moore’s Law, system-on-chips (SoCs) should continually become more complex and integrate more components, enabled by each reduction in silicon technologies. However, power consumption does not follow the linear path implied here due to increasing leakage in deep sub-micron technologies. Hence, new power management techniques are needed to reduce power dissipation as much as […]

Extending UPF for incremental growth

Erich Marschner Accellera’s Unified Power Format (UPF) is in production use today, delivering the low-power system-on-chip (SoC) designs that are so much in demand. Building upon that success, IEEE Std 1801-2009 [UPF] offers additional features that address the challenges of low-power design and verification. These include more abstract specifications for power supplies, power states, and […]

The art of low-power physical design

The architectures that underpin today’s traditional place-and-route tools are showing their age, largely because their static timing analysis engines cannot handle more than two mode/corner scenarios. Thus limited, the software struggles to effectively implement low-power design techniques beyond such established concepts as clock gating and multiple threshold voltages. Designers run into difficulties when trying to […]