September 11, 2018

Gandharv Bhatara looks at how the OPC and RET elements of Calibre are getting ready for the EUV age.

August 13, 2018

Dina Medhat describes what you need to know about the types of waiver strategy that can be applied.

July 9, 2018

A hierarchical methodology removes DFT from the critical path for large designs. The methodology is compatible with other techniques such as channel sharing, which can further reduce ATPG turn-around time and test cost.

June 18, 2018

How to use formal fault pruning, injection and sequential equivalency checking to meet the FMEA analysis requirements of the functional safety standard.

June 11, 2018

An introduction to how virtual emulation has fueled the application of co-modeling for complex design verification.

May 9, 2018

Learn how planning and upfront knowledge of the challenges ahead can open up what has seemed a challenging task.

April 23, 2018

Why design data integrity matters from cell design to tapeout. These techniques will help ensure your validation process is as comprehensive as possible.

April 9, 2018

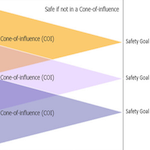

A new version of the automotive safety standard arrives later this year. Review the main updates and see how it will combine with the incoming SOTIF autonomous driving standard.

March 19, 2018

In an exclusive interview, Lauro Rizzatti discusses the increasing verification challenges for drone SoCs with Bo Shen, founder of fabless specialist Artosyn.

March 9, 2018

Still using custom layout or place and route tools here? Ditch that time-consuming practice for a real database merge flow.